ISSN 0352-9045

Journal of Microelectronics, Electronic Components and Materials **Vol. 49, No. 2(2019), June 2019**

Revija za mikroelektroniko, elektronske sestavne dele in materiale **Ietnik 49, številka 2(2019), Junij 2019**

# Informacije MIDEM 2-2019 Journal of Microelectronics, Electronic Components and Materials

### VOLUME 49, NO. 2(170), LJUBLJANA, JUNE 2019 | LETNIK 49, NO. 2(170), LJUBLJANA, JUNIJ 2019

Published quarterly (March, June, September, December) by Society for Microelectronics, Electronic Components and Materials - MIDEM. Copyright © 2019. All rights reserved. | Revija izhaja trimesečno (marec, junij, september, december). Izdaja Strokovno društvo za mikroelektroniko, elektronske sestavne dele in materiale – Društvo MIDEM. Copyright © 2019. Vse pravice pridržane.

### Editor in Chief | Glavni in odgovorni urednik

Marko Topič, University of Ljubljana (UL), Faculty of Electrical Engineering, Slovenia

### Editor of Electronic Edition | Urednik elektronske izdaje

Kristijan Brecl, UL, Faculty of Electrical Engineering, Slovenia

#### Associate Editors | Odgovorni področni uredniki

Vanja Ambrožič, UL, Faculty of Electrical Engineering, Slovenia Arpad Bürmen, UL, Faculty of Electrical Engineering, Slovenia Danjela Kuščer Hrovatin, Jožef Stefan Institute, Slovenia Matija Pirc, UL, Faculty of Electrical Engineering, Slovenia Matjaž Vidmar, UL, Faculty of Electrical Engineering, Slovenia

#### Editorial Board | Uredniški odbor

Mohamed Akil, ESIEE PARIS, France Giuseppe Buja, University of Padova, Italy Gian-Franco Dalla Betta, University of Trento, Italy Martyn Fice, University College London, United Kingdom Ciprian Iliescu, Institute of Bioengineering and Nanotechnology, A\*STAR, Singapore Marc Lethiecq, University of Tours, France Teresa Orlowska-Kowalska, Wroclaw University of Technology, Poland Luca Palmieri, University of Padova, Italy Goran Stojanović, University of Novi Sad, Serbia

#### International Advisory Board | Časopisni svet

Janez Trontelj, UL, Faculty of Electrical Engineering, Slovenia - Chairman Cor Claeys, IMEC, Leuven, Belgium Denis Đonlagić, University of Maribor, Faculty of Elec. Eng. and Computer Science, Slovenia Zvonko Fazarinc, CIS, Stanford University, Stanford, USA Leszek J. Golonka, Technical University Wroclaw, Wroclaw, Poland Jean-Marie Haussonne, EIC-LUSAC, Octeville, France Barbara Malič, Jožef Stefan Institute, Slovenia Miran Mozetič, Jožef Stefan Institute, Slovenia Stane Pejovnik, UL, Faculty of Chemistry and Chemical Technology, Slovenia Giorgio Pignatel, University of Perugia, Italy Giovanni Soncini, University of Trento, Trento, Italy Iztok Šorli, MIKROIKS d.o.o., Ljubljana, Slovenia Hong Wang, Xi´an Jiaotong University, China

### Headquarters | Naslov uredništva

Uredništvo Informacije MIDEM MIDEM pri MIKROIKS Stegne 11, 1521 Ljubljana, Slovenia T. +386 (0)1 513 37 68 F. + 386 (0)1 513 37 71 E. info@midem-drustvo.si www.midem-drustvo.si

Annual subscription rate is 160 EUR, separate issue is 40 EUR. MIDEM members and Society sponsors receive current issues for free. Scientific Council for Technical Sciences of Slovenian Research Agency has recognized Informacije MIDEM as scientific Journal for microelectronics, electronic components and materials. Publishing of the Journal is cofinanced by Slovenian Research Agency and by Society sponsors. Scientific and professional papers published in the journal are indexed and abstracted in COBISS and INSPEC databases. The Journal is indexed by ISI® for Sci Search®, Research Alert® and Material Science Citation Index™. |

Letna naročnina je 160 EUR, cena posamezne številke pa 40 EUR. Člani in sponzorji MIDEM prejemajo posamezne številke brezplačno. Znanstveni svet za tehnične vede je podal pozitivno mnenje o reviji kot znanstveno-strokovni reviji za mikroelektroniko, elektronske sestavne dele in materiale. Izdajo revije sofinancirajo ARRS in sponzorji društva. Znanstveno-strokovne prispevke objavljene v Informacijah MIDEM zajemamo v podatkovne baze COBISS in INSPEC. Prispevke iz revije zajema ISI® v naslednje svoje produkte: Sci Search®, Research Alert® in Materials Science Citation Index™.

Design | Oblikovanje: Snežana Madić Lešnik; Printed by | tisk: Biro M, Ljubljana; Circulation | Naklada: 1000 issues | izvodov; Slovenia Taxe Percue | Poštnina plačana pri pošti 1102 Ljubljana

Journal of Microelectronics, Electronic Components and Materials vol. 49, No. 2(2019)

# Content | Vsebina

| Original scientific papers                                                                                                                  |     | Izvirni znanstveni članki                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M. T. I. Badal, M. Bin I. Reaz,<br>M. A. S. Bhuiyan, C. A. Dhawale:<br>Nano CMOS Charge Pump for Readerless RFID PLL                        | 53  | M. T. I. Badal, M. Bin I. Reaz,<br>M. A. S. Bhuiyan, C. A. Dhawale:<br>Nano CMOS črpalka energije za RFID PLL brez<br>čitalca                                       |

| W. Tangsrirat:<br>Linearly Tunable CMOS Voltage Differencing<br>Transconductance Amplifier (VDTA)                                           | 61  | W. Tangsrirat:<br>Linearno nastavljiv CMOS napetostni<br>transkonduktančni diferencialni ojačevalnik (VDTA)                                                         |

| X. Huang:<br>Simulation on the Interfacial Singular Stress-strain<br>Induced Cracking of Microelectronic<br>Chip Under pPower On-off Cycles | 69  | X. Huang:<br>Simulacija razpok mikroelektronskega čipa zaradi<br>posameznih mejnih stresov pri ciklih vklapljanja<br>napajanja                                      |

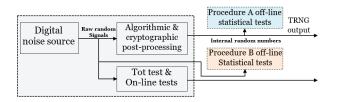

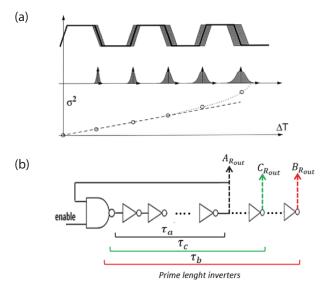

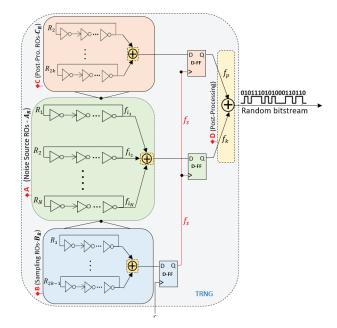

| A. M. Garipcan, E. Erdem:<br>Implementation of a Digital TRNG Using Jitter<br>Based Multiple Entropy Source on FPGA                         | 79  | A. M. Garipcan, E. Erdem:<br>Uporaba digitalne TRNG na FPGA z uporabo več<br>entropijskih virov na osnovi tresenja                                                  |

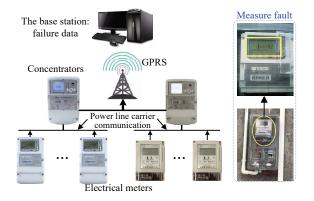

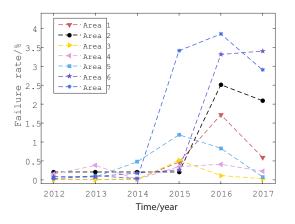

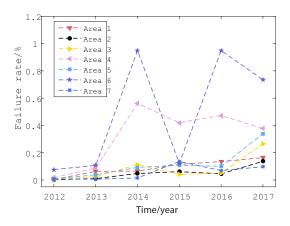

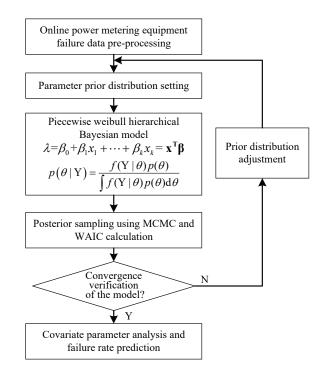

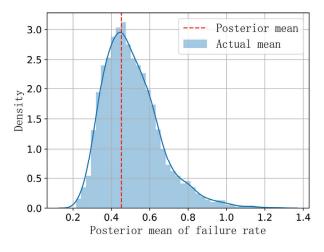

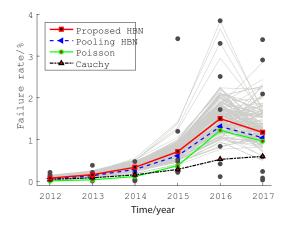

| D. Cheng, P. Zhang, F. Zhang, J. Huang:<br>Fault Prediction of Online Power Metering<br>Equipment Based on Hierarchical<br>Bayesian Network | 91  | D. Cheng, P. Zhang, F. Zhang, J. Huang:<br>Napovedovanje izpada na opremi merjenja moči<br>na osnovi hierarhične Bayesianove mreže                                  |

| M. Možek, B. Pečar, D. Resnik, D. Vrtačnik:<br>Piezoelectric Micropump Driving Module with<br>Programmable Slew-Rate and Dead-Time          | 101 | M. Možek, B. Pečar, D. Resnik, D. Vrtačnik:<br>Krmilni modul piezoelektričnih mikročrpalk z<br>nastavljivo hitrostjo spremembe in mrtvim časom<br>krmilnega signala |

| Doctoral theses on Microelectronics, Electronic<br>Components and Materials in Slovenia in 2018                                             | 113 | Doktorske disertacije na področju mikroelektron-<br>ike, elektronskih sestavnih delov in materialov v<br>Sloveniji v letu 2018                                      |

| Front page:<br>Body teperature load<br>(X. Huang)                                                                                           |     | Naslovnica:<br>Temperaturna obremenitev<br>(X. Huang)                                                                                                               |

https://doi.org/10.33180/InfMIDEM2019.201

Journal of Microelectronics, Electronic Components and Materials Vol. 49, No. 2(2019), 53 – 60

# Nano CMOS Charge Pump for Readerless RFID PLL

Md Torikul Islam Badal<sup>1</sup>, Mamun Bin Ibne Reaz<sup>2</sup>, Mohammad Arif Sobhan Bhuiyan<sup>3</sup>, Chitra A. Dhawale<sup>4</sup>

<sup>1</sup>RMIT University, Department of Electronic and Telecommunication Engineering, Melbourne, Victoria, Australia

<sup>2</sup>University Kebangsaan Malaysia, Department of Electrical, Electronic and System Engineering, Bangi, Selangor, Malaysia

<sup>3</sup>Xiamen University Malaysia, Department of Electrical and Electronics Engineering, Sepang, Selangor, Malaysia

<sup>4</sup>P.R.Pote College of Engineering and Management, Department of MCA, Amravati, Maharashtra, India

**Abstract:** Readerless RFID has become more significant for reliable wireless communication. The Phase Locked Loop (PLL) is among the most crucial functional block in the Readerless RFID where the PLL performance greatly depends on the Charge Pump (CP). Conventional CP circuits suffer from current mismatching characteristics which generate phase offset and spurs in the PLL output signals. To overcome these problems, the CP current mismatch has to be minimized. An enhanced CP circuit with zero current mismatch is presented in this article adopting an ideal current mirror technique and an additional inverter to provide a rail-to-rail voltage. The post-layout simulation shows that the proposed CP maintains the steady current over a wide range of output voltage from 0.1-1.8 V consuming the substantially lower power of 0.178 µW. The CP circuit is designed in 130 nm CMOS process that operates at 1.8 V, and the core occupies 17 x 59.5 µm2. The proposed CP will be a good solution for low voltage, high-frequency PLL structure which suffers from poor performance.

Keywords: Charge pump; CMOS; Current mismatch; PLL; RFID

# Nano CMOS črpalka energije za RFID PLL brez čitalca

**Izvleček:** RFID brez čitalca so postali pomembni za zanesljivo brezžično komunikacijo. Eden izmed kritičnih funkcijskih blokov RFID brez čitalca je, od črpalke energije (CP) odvisna, fazno sklenjena zanka (PLL). Konvencionalni CP trpijo z neuravnoteženo tokovno karakteristiko, ki vpliva na izhodni signal PLL. V izogib tem problemom je potrebno minimizirati CP. Članek opisuje izboljšan CP z ničelno tokovno neuravnoteženostjo z uporabo tehnike idealnega zrcaljenja toka in dodatnega inverterja za zagotavljanje napajanja. Simulacije nakazujejo da CP vzdržuje konstantni tok čez široko območje napajalne napetosti od 0.1-1.8 V in porabijo izredno malo moč 0.178 μW. Vezje je zasnovano v 130 nm CMOS tehnologiji pri napajalni napetosti 1.8 V. Velikost jedra je 17.0 x 59.5 μm2. Predlagana rešitev je dobra za uporabo v nizkonapetostnihvisokofrekvenčnih PLL strukturah z nizkim učinkom.

Ključne besede: črpaka energije; CMOS; tokovno neujemanje; PLL; RFID

\* Corresponding Author's e-mail: torikul.uniten@gmail.com;

## 1 Introduction

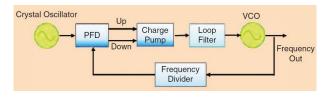

At present, Readerless RFID systems are experiencing rapid growth because of the advancement of the wireless communication system. RFID is an identification system, where data is transferred/received via radio frequency among antenna, reader, and transponder. In an RFID system, electronic product code which is also known as the identification code is attached to an object for tracking. A frequency synthesizer (FS) is a feedback system that produces one or more frequencies from a single or several frequency sources. Charge pump based PLL (CPPLL) is broadly used in a wireless communication systems for frequency synthesis; especially in radio, telecommunications and other electronic applications due to its simple feedback system [1, 2]. CPPLL is preferred because of low bias current [3, 4], low static phase offset [5-7] and large system gain [8, 9]. Furthermore, it performs the key role to ensure the stability of frequency synthesis [10, 11]. The PLL is generally composed of a phase frequency detector (PFD), a charge pump (CP), a loop filter (LF), a voltagecontrolled oscillator (VCO) and a frequency divider as depicted in Figure 1. Among all the functional blocks, CP is the most crucial block which significantly contributes to boosting the PLL's overall performance and stability. It changes the digital signal originating from PFD into an analog signal which in turn controls the VCO frequency [12]. The output voltage of the charge pump must be fixed when the PLL goes into a locked state at a specific frequency. Any change of that voltage results in frequency offset. [5, 13, 14]. In this regard, it is imperative to design a charge pump circuit that can generate a steady output current and can produce a superbly matched current with zero error in CPPLL.

Figure 1: A Basic Block Diagram of CPPLL [4]

Charge pump (CP) is the subsequent stage to the PFD, i.e., the output (UP and DWN) signals of the PFD are fed to the CP circuit. The key principle of a charge pump is to translate the logic states of the PFD into suitable analog signals to control the voltage-controlled oscillator (VCO) through a loop filter. Fundamentally, the charge pump is made up of current sources and switches as shown in Figure 2. The output currents from the CP is usually filtered by a low pass filter (LPF) that converts the charge pump current to an equivalent control voltage for the VCO.

The conventional CP circuit consists of a charge and a discharge digital output current source, ICH and IDIS respectively described in Figure 2. A couple of transistor-based switches control both ICH and IDIS of the PFD. The two switches drive the loop filters and convert the output signals of the PFD to an analog voltage signal, Vcntrl, to tune the frequency of the VCO. The basic CP circuit suffers from many disadvantages, and as a consequence, several charge pump architectures have

Figure 2: The basic concept of a charge pump circuit.

been reported with their pros and cons in the literature [14].

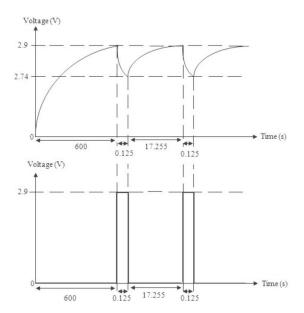

The imperfection of a CP can be estimated by the current mismatch, timing mismatch, power consumption, and charge sharing. But the current mismatch is the most vital parameter which leads the PLL performance. The current mismatch implies the magnitude dissimilarity between charging and discharging current which is a crucial concern for the CP design [8, 15]. Figure 3 represents the charging and discharging time diagram of a charge pump circuit.

**Figure 3:** Charging and discharging time diagram of a charge pump circuit

The issues of current mismatch and leakage current introduce the phase error problem and produce PLL's reference spur [16, 17]. The current mismatch and leakage can be characterized as:

$$\Delta \emptyset = 2\pi \left( \Delta \emptyset_{\text{timing}} + \Delta \emptyset_{\text{mismatch}} + \Delta \emptyset_{\text{leakage}} \right)$$

(1)

Where,  $\Delta \emptyset$ ,  $\Delta \emptyset$  timing,  $\Delta \emptyset$  mismatch, and  $\Delta \emptyset$  leakage, are the phase error, timing mismatch, current mismatch and leakage current of the CP circuit, respectively. Equation 1 shows that the current mismatch is directly associated with phase error and PLL's reference spur which is otherwise called dynamic jitter [7]. The measure of the reference spurs Pr can be defined by [18]

$$Pr = 20 \log \left(\frac{\Delta \emptyset f_{\rm BW}}{\sqrt{2 f_{\rm REF}}}\right) - 20 \log \left(\frac{f_{\rm REF}}{f_{\rm PL}}\right) \left[dBc\right] \tag{2}$$

and the loop bandwidth, f<sub>RW</sub> is given by

$$f_{BW} = I_{CP} K_{VCO} R / (2\pi N) \tag{3}$$

Where, Pr is the PLL reference spur,  $\boldsymbol{f}_{_{REF}}$  refer the reference frequency of the phase frequency detector (PFD),  $f_{_{BW}}$  stands for the loop bandwidth,  $\Delta Ø$  is the phase error, and  $f_{PL}$  is the Loop filter's pole frequency.  $I_{CP}$  stands for the CP current flow,  $K_{vco}$  refers to the VCO gain, R is the loop filter's resistor value where N is the divider value. Equation (2) describes that Pr is proportional to the loop bandwidth ( $f_{_{BW}}$ ) and phase error ( $\Delta Ø$ ). Which means, the reference spurs can be reduced by increasing the reference frequency  $(\boldsymbol{f}_{_{REF}})$  and minimizing the phase error ( $\Delta Ø$ ) and loop bandwidth ( $f_{BW}$ ). Therefore, a CP design is required, which can reduce the current mismatch and maintain the constant current over a wide range of output voltage. By decreasing the current variation and mismatch, the performance of CP can be significantly improved. This reduces the PLL's spurs and static phase offset. Therefore, a CP that can reduce the current mismatch and maintains the currents constant across a wide range of output voltage is the key block for creating an optimum CPPLL system.

Based on the literature review the current mismatch issue in CP design can be overcome in many ways [20-23]. Low-voltage cascade topology [19, 20] is a conventional approach for minimizing the current mismatch at the cost of high output resistance. With this conventional approach, the current mismatching features in these CPs [19, 20] are scaled down to 2%. Besides, current mismatching is reduced to <1% in [6, 8] by integrating operational amplifiers (Op-amp) technique. This method integrates a negative feedback amplifier along with op-amp where Op-amp controls the voltage node maintaining high amplifier gain and provides the advantage of the large input voltage of charge and discharge currents [21]. The current mismatch in [7] is reduced by executing a differential CP with an active loop filter (LF) and common-mode feedback scheme. This scheme integrated an op-amp, an analog adder, and a reference voltage circuit. Huh et al [22] proposed a replica CP where the current mismatch is compensated down to 1% by utilizing a bias generator. But, it requires a complicated circuit and creates a longer locking time. An unexpected current mismatch occurs in this architecture because of the fabrication mismatch between two CPs.

The variables that are responsible for current mismatch are current sharing, charge injection and clock feed. Controlling the switching circuit by the transistor causes charge injection. Charge injection arises when the transistor is utilized to govern the switching circuit and produce limited capacitance to the current sources [20, 23]. Keeping in mind the end goal to diminish current mismatch and current variation, the power consumption and the output voltage dynamic range must also be considered. Besides, the approach with double stage op-amps in three rail-to-rail amplifiers is competent and established for reducing the current mismatch. It adjusts the current mirror gate bias that results in matching the output of the switch current with the drain current. Thus, it reduces the static phase offset significantly and minimizes the current mismatch. This article proposes an improved CP design in 130 nm CMOS process based on the current mirror method employing an inverter at the gates of transistors for providing a rail-to-rail voltage swing to accomplish adequate current matching.

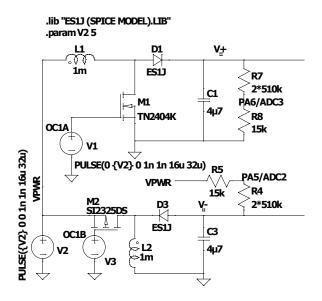

## 2 Proposed Charge Pump Circuit

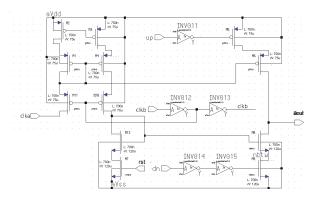

A modified CP is designed based on current mirror technique integrating an inverter at the gates of the transistor to provide a rail-to-rail voltage swing that reduces the current mismatch and the voltage mismatch problem. The recommended CP circuit with current mirrors technique is presented in figure 4. The two current sources I1 and I2 are implemented as current mirrors. I1 and Up utilize PMOS transistors while I2 and Down use NMOS transistors. To increase the output resistance, the lengths of all transistors have been set to twice the minimal size at 700 nm [8]. To decrease the required amount of VGS the transistors with large widths were chosen so that the circuit could perform near the rail. An inverter is added at the PMOS transistor because its input must be inverted. Two inverters were set at the Dn gate to match the capacitances at the gates. Transistors M5 and M9 are connected to the node "aout" through the mirror transistors M6 and M8. This helps to decrease the impact of charge sharing. Moreover, the current mirror approach ensures that the charge and discharge currents retain a precise value for large voltage and guarantee that the Up and the Dn inputs are matched well. To assure both currents are equivalent, the current mirror is utilized for replicating current Up and current Dn from a single current source.

Figure 4: The proposed CP circuit based on current mirrors technique with inverters

## 3 Results and Discussions

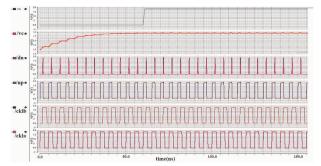

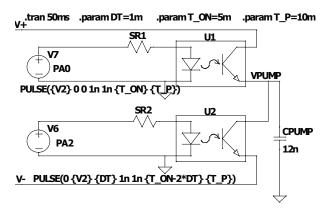

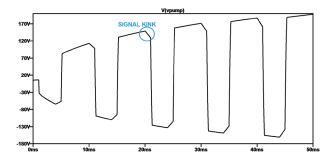

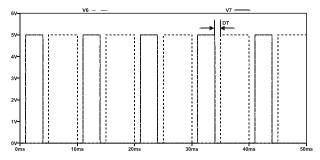

The post-layout results of the designed CP circuit are depicted in figure 5-9. From the post-layout simulation, it is shown that the proposed CP can reach maximum output voltage of 1.8 V. Generally, schematic simulation is viewed as an ideal case, while the post-layout simulation is considered the actual case, which incorporates reverse charge sharing or body impact and parasitic capacitance. The post-layout simulation output voltage result is identical in comparison with the schematic simulation. The output results of the designed CP are verified using ELDONET simulators in TSMC 130 nm CMOS process. Usually, the voltage amplitudes of "clka" and "clkb" are equal to the power supply (VDD). The simulation parameters are used at 10 MHz pumping clock frequency along with 0.1 pF pumping capacitor and the input voltage connected to a 1.8V power supply. It is found that the designed CP circuit is successfully pumped up and down for the output voltage range from 0.1V to 1.8V. Figure 5 shows that when the reset transistor is disconnected, "clkb" is set to be delayed by 1.5 ns. As a result, the output waveform is observed to be charged up to Vdd, and the Up signal is wider than the Dn signal.

**Figure 5:** Post layout Result of Proposed CP Circuit: Pumping-Up @ (Vdd = 1.8 V, f = 10MHz)

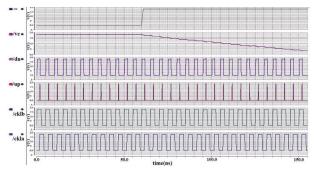

Figure 6 clearly shows the voltage trend at the Vc node moving down, and the Dn pulse is wider than the Up pulse. When the reset transistor is connected, and "clka" signal is delayed by 1.5 ns. Figure 7 is the zoomed plot of the simulation where the Dn and Up signals are perfectly in phase with the pulse widths being 224.6 ps (Dn) and 222.8ps (Up). The voltage of pumping-up and pumping down for the modified CP is in the range between 0.1 V and 1.8V.

**Figure 6:** Post layout of the proposed CP Circuit: Pumping-down@ (Vdd = 1.8 V, f = 10 MHz).

**Figure 7:** Simulation result of proposed CP Circuit (When both clock sources set are perfectly in-phase)

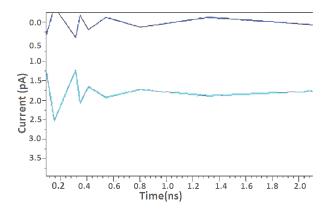

Figure 8 describes the current matching of the designed charge pump circuit, and it is observed that the maximum value for the current mismatch is zero. The curve (Figure 8 results) is taken from the Mentor Graphics EZwave analysis window. In EZwave window, the current mismatch is shown in the form of the graph instead of a percentage. The cyan and Blue, both graphs represent the current (Y-axis) graph with respect to time(X-axis). It can be seen in the figure that, the changes in the current of both graphs with respect to time (X-axis) is almost the same. There is no difference in current fluctuation which represent the Zero current mismatch. The zero current mismatches are achieved because of the low voltage NMOS cascade mirror technique and the addition of the M5 and M9 which are connected to the node "aout" through the mirror

transistors M6 and M8. For the PMOS switched mirror, the low-voltage cascade current mirror is connected to Gnd and for the NMOS switched mirror VDD is chosen as these are the values of Up and Dn signals at the lock which results in higher matching. Figure 8 proves that this modified scheme manages to decrease the effects of charge sharing and the current mismatch as well.

Figure 8: Current Up and Dn Plots (current matching)

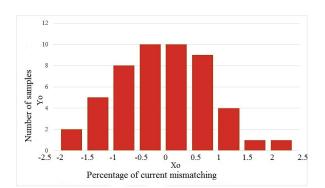

Statistical analysis is very important in the absence of measured results. The Monte Carlo analysis of the proposed CP is presented in Figure 9 as a histogram representation. For 50 runs, the actual current mismatch of the proposed CP is zero. But randomly it shows the current mismatch varies from -2 to 2.5% which is very negligible. Besides, according to the netlist analysis of Monte Carlo simulation, the results showed that the current mismatch performance of the CP was stable around zero percentage. The Monte Carlo analysis was performed in the Mentor graphics environment.

The performance comparison among proposed CMOS charge pump circuit and recently reported other CMOS CP designs based on different input and output parameters are given in table 1.

**Figure 9:** Monte Carlo simulation of current mismatch of the proposed CP

From table 1, it can be noted that the performance of the charge pump can be assessed by the current mismatch and power dissipation. For easy integration on a compact die, the designer tends to choose a simple circuit architecture for the charge pump. It can be observed from table 1 that the proposed CP circuit exhibits a many-fold reduction in both current mismatch and power dissipation compared to others designs. The major advancements have been achieved in the current mismatch of the proposed CP. The maximum current mismatch (<7%) occurs in [6] in table 1. The channel length modulation effect, the mismatch between PMOS and NMOS transistors and CMOS process variations cause this high current mismatch. Park et al.

Table 1: Comparison of proposed CMOS CP performance with other CMOS CP architectures.

| Publication<br>year and Ref. | CMOS CP scheme                    | CMOS<br>process<br>(µm) | Supply<br>voltage<br>(V) | Output<br>voltage<br>(V) | Current<br>mismatch | Power<br>consumed |

|------------------------------|-----------------------------------|-------------------------|--------------------------|--------------------------|---------------------|-------------------|

| [23]<br>[2011]               | Rail-to-rail op-amp               | 0.18                    | 1.8                      | 0.4-1.7                  | 0.4%                | 0.9 mW            |

| [24]<br>[2013]               | Basic CP-PLL                      | 0.18                    | 1.8                      | 0.7-1.3                  | 5%                  | 1.6 mW            |

| [8]<br>[2013]                | Digital calibration technique     | 0.18                    | 1.8                      | -                        | 1%                  | 6.2 mW            |

| [11]<br>[2014]               | Dickson CP with CTS's             | 0.18                    | 1.8                      | 1.8-4.2                  | -                   | 1.2 mW            |

| [25]<br>[2015]               | Feedback Op-amp                   | 0.18                    | 1.8                      | 0.25- 1.                 | <5%                 | 13 mW             |

| [26]<br>[2016]               | Wide-swing current mirror         | 0.18                    | 1.8                      | 0.3- 1.5                 | 0.32%               | 0.38 mW           |

| [6]<br>[2017]                | Feedback loop                     | 0.18                    | 1.8                      | 0.3-1.4                  | <7%                 | 740 μW            |

| Proposed<br>CMOS CP          | Current mirror and chain inverter | 0.13                    | 1.8                      | 0.1-1.8                  | 0%                  | 0.178 μW          |

[25] suggested architecture also suffers from a high current mismatch of <5% because of the finite output impedance of the current source and highest power consumption of 13 mW. A high power consumption and current mismatch are achieved at the same time by Zhiqun et al. [6] Implementing a rail-to-rail operational amplifier. The recently reported CP proposed by Lozada et al. [8] managed to achieve a good current mismatch of 0.32% and less power consumption compared to [6, 11]. Therefore, compared to results mentioned in table 1, it can be concluded that the proposed charge pump circuit has the lowest power consumption of 0.178 mW and provides the lowest (zero) current mismatch by using the current mirror and chain inverter technique which leads to a high-performance CPPLL. Moreover, in the case of output voltage, it is clear that the output voltage of the proposed CP is significantly higher than those of all previously designed [24-26] charge pumps. This signifies the notable enhancement in output over those achieved in previous researches.

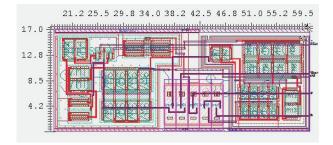

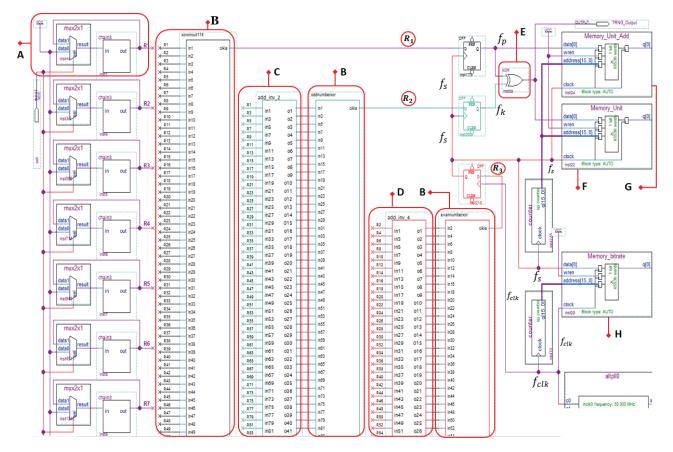

Figure 10 presents the complete layout of the proposed CP using TSMC 130 nm CMOS process. The dimension of the designed CP layout is 17 x 59.5  $\mu$ m. Since the CP circuit covers only a small area, it reduces the cost as well. In this design, the triple-well isolated MOSFET structure has been used. Multi-finger structure has also been implemented for transistors with large aspect ratios to keep the conductivity within acceptable limits. The layout is designed for the convenience of cascading an extra pumping stage to the output voltage for additional improvement. Fabrication in CMOS technology makes it a good candidate for integration with other CMOS-based devices or modules in telecommunications and other electronic applications.

Figure 10: Layout diagram of proposed CMOS CP using TSMC 130 nm CMOS technology

## 4 Conclusions

The CP output parameters have a large impact on PLL performance. To meet the current demand of low power consumption, zero current mismatch and zero

net charges, an enhanced charge pump circuit implementing the current mirror technique along with an inverter is presented in this research. The low voltage NMOS cascade mirror technique and additional transistors that are connected to the output node through the mirror transistors manage to achieve the lowest current mismatch. The post-layout result shows that the proposed charge pump circuit provides zero current mismatch at 1.8 V supply voltage with a pumping capacitor of 0.1 pF and consumes only 0.178  $\mu$ W. The charge pump circuit is suitable for Readerless RFID applications and can be widely used in various low power wireless electronic devices such as a transceiver; disk read/write channels for high-speed data transmission, clock synthesis, synchronization, jitter reduction, etc.

# **5** Conflicts of Interest

"The authors declare no conflict of interest."

## 6 Acknowledgment

This research is financially supported by University Kebangsaan Malaysia. Project code: [AP-2017-008/1].

## 7 References

Jiang X., Yu X., Moez K., Elliott D. High-Efficiency Charge Pumps for Low-Power On-Chip Applications, IEEE journal of Solid State Circuit, 2018, 65(3): 1143 – 1153.

https://doi.org/10.1109/tcsi.2017.2759767

Badal MT I, Reaz M B I, Bhuiyan M, Kamal N, CMOS Transmitters for 2.4-GHz RF Devices: Design Architectures of the 2.4-GHz CMOS Transmitter for RF Devices, IEEE Microwave Magazine, 2019, 20 (1), pp: 38-61.

### https://doi.org/10.1109/mmm.2018.2875607

- Yun G S, KOK S L, Rahman, M B, Development of self-powered thermoelectric based RF transmitter circuit, IEEE International conference on Power and Energy, Nov, 2016, Melaka, Malaysia. <u>https://doi.org/10.1109/pecon.2016.7951602</u>

- Badal M T I, Reaz M B I, Jalil Z and Bhuiyan M, Low Power High-Efficiency Shift Register Using Implicit Pulse-Triggered Flip-Flop in 130 nm CMOS Process for a Cryptographic RFID Tag, Electronics, 2016, 5(4), pp: 92.

https://doi.org/10.3390/electronics5040092 5. Badal M T I, Reaz M B I, Yeng L S, Bhuiyan M, Advancement of CMOS transimpedance amplifier for optical receiver, Transactions on Electrical and Electronic Materials, 2018, 20(2), pp:73-84. https://doi.org/10.1007/s42341-018-00092-5

- 6. Estebsari M, Gholami M, Ghahramanpour M. A Novel Charge Pump with Low Current for Low-Power Delay-Locked Loops, *Circuits System and Signal Processing*, 2017, 36(9), pp. 3514–3526. https://doi.org/10.1007/s00034-016-0481-6

- Chen Y, Mak P I, Zhou Y. Self-tracking charge pump for fast-locking PLL, *Electronics letters*, 2010, 46(11), pp. 755-757. https://doi.org/10.1049/el.2010.3562

- 8. Jeong C H, Kim KY, Kwon C K, Kim H, Kim S W. Digital calibration technique using a signed counter for charge pump mismatch in phase-locked loops, *IET Circuits, Devices, Systems*, 2013, 7(6), pp. 313-318.

https://doi.org/10.1049/iet-cds.2013.0011

- 9. Choi Y S, Han D H. Gain-boosting charge pump for current matching in phase-locked loop, *IEEE Transactions on Circuits and Systems II, Express Briefs*, 2006, 53(10), pp. 1022-1025. https://doi.org/10.1109/tcsii.2006.882122

- 10. Zaziabl A. Low power 1 GHz charge pump phaselocked loop in 0.18 μm CMOS process, *Proceedings of the 17th International Conference Mixed Design of Integrated Circuits and Systems-(MIXDES)*, 2010, pp. 277-282.

- 11. Kailuke C, Agrawal P, Kshirsagar R. Design of phase frequency detector and charge pump for low voltage high frequency PLL, *IEEE International Conference On Electronic Systems, Signal Processing and Computing Technologies (ICESC)*, 2014. pp. 74-78.

https://doi.org/10.1109/icesc.2014.21

- Badal M T I, Reaz M B I, Farayez A, Ramli S, Kamal N, "Design of a low-power CMOS Level Shifter for low-delay SoCs in silterra 0.13 μm CMOS process", Journal of Engineering Science and Technology Review, 2017, 10(4), pp. 10-15. https://doi.org/10.25103/jestr.104.02

- 13. Park J, Kim N, Won D, Choi H. High performance two-stage charge-pump for spur reduction in CMOS PLL, Proceeding of the 11th IEEE International Multi-Conference on Signal, System and Device (SSD), 2014, pp. 1-7.

https://doi.org/10.1109/ssd.2014.6808749

Badal M T I, Mashuri M B, Reaz M B I, Kamal N, Hashim F H, Low power high speed current comparator using 130nm CMOS technology, International Conference on Advances in Electrical, Electronic and System Engineering, 2016, pp: 72-76, Malaysia.

https://doi.org/10.1109/icaees.2016.7888012

15. Gupta J A, Sangal A, Verma H. High speed CMOS charge pump circuit for PLL applications using

90nm CMOS technology, *Proceedings of the IEEE* world Congress on Information and Communication Technologies (WICT), 2011, pp. 346-349. https://doi.org/10.1109/wict.2011.6141270

- 16. Paemel M V. Analysis of a charge-pump PLL, a new model. *IEEE Transactions on communications*, 1994, 42(7), pp. 2490-2498. https://doi.org/10.1109/26.297861

- 17. Cheng S, Tong H, Martinez J S, Karsilayan A I. Design and Analysis of an Ultrahigh-Speed Glitch-Free Fully Differential Charge Pump With Minimum Output Current Variation and Accurate Matching, *IEEE Transactions on Circuits and Systems II, Express Briefs*, 2006, 53(9), pp. 843-47. https://doi.org/10.1109/tcsii.2006.879100

- 18. Rhee W. Design of high-performance CMOS charge pumps in phase-locked loops, *Proceeding of the 1999 IEEE International Symposium on Circuits and Systems (Florida, USA)*, 1999, pp. 545-548. https://doi.org/10.1109/iscas.1999.780807

- 19. Larsson P. A 2-1600-MHz CMOS clock recovery PLL with low-Vdd capability, *IEEE Journal of Solid-State Circuits*, 1999, 34(12), pp. 1951-60. https://doi.org/10.1109/4.808920

- Ahola R, Halonen, K. A 1.76-GHz 22.6-mW ΔΣ fractional-n frequency synthesizer, *IEEE Journal of Solid-State Circuits*, 2003. 38(1), pp. 138-140. <u>https://doi.org/10.1109/jssc.2002.806261</u>

- 21. Lee J S, Keel M S, Lim S I, Kim S. Charge pump with perfect current matching characteristics in phase-locked loops, *Electronics Letters*, 2000, 36(23), pp. 1907-1908. https://doi.org/10.1049/el:20001358

- 22. Huh H. et al, A CMOS dual-band fractional-N synthesizer with reference doubler and compensated charge pump, *Proceeding of the IEEE International Solid-State Circuits Conference (ISSCC), Digest of Technical Papers.* 2004, pp. 100-101. https://doi.org/10.1109/isscc.2004.1332613

- 23. Zhiqun L, Shuangshuang Z, Ningbing H. Design of a high-performance CMOS charge pump for phase-locked loop synthesizers, *Journal of Semiconductors*, 2011, 32(7), pp. 075007. https://doi.org/10.1088/1674-4926/32/7/075007

- 24. Yoshimura T, Iwade S, Makino H, Matsuda, Y. Analysis of pull-in range limit by charge pump mismatch in a linear phase-locked loop, *IEEE Transactions on Circuits and Systems I, Regular Papers*, 2013, 60(4), pp. 896-907.

https://doi.org/10.1109/tcsi.2012.2215393

25. Park J W, Choi H Y, Kim N S. Two-stage feedbacklooped charge-pump for spur reduction in CMOS PLL, *Analog Integrated Circuits and Signal Processing*, 2015, 83(2), pp. 143-148. https://doi.org/10.1007/s10470-015-0517-z 26. Lozada O, Espinosa G. A charge pump with a 0.32% of current mismatch for a high speed PLL, Analog Integrated Circuits and Signal Processing, 2016, 86(2), pp. 321-326.

https://doi.org/10.1007/s10470-015-0676-y

Copyright © 2019 by the Authors. This is an open access article distributed under the Creative Com-

mons Attribution (CC BY) License (https://creativecommons.org/licenses/by/4.0/), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Arrived: 18. 11. 2018 Accepted: 14. 05. 2019

Journal of Microelectronics, Electronic Components and Materials Vol. 49, No. 2(2019), 61 – 68

# Linearly Tunable CMOS Voltage Differencing Transconductance Amplifier (VDTA)

Worapong Tangsrirat

# Faculty of Engineering, King Mongkut's Institute of Technology Ladkrabang (KMITL), Bangkok, Thailand

**Abstract:** This paper proposes an alternative way to implement a linearly tunable CMOS voltage differencing transconductance amplifier (VDTA). It has been designed by using the floating current source (FCS) and the current squaring circuit. The circuit achieves its linear tunability by squaring the long-tail biasing current of the FCS. In this way, the transconductance gains of the proposed CMOS VDTA can be varied linearly through adjusting the DC bias currents. As an application example, the proposed VDTA is used in the design of an actively tunable voltage-mode multifunction filter. The derived filter possesses the following desirable properties: simultaneous realization of three standard filter functions; employment of only two grounded capacitors; and electronic tunability of the natural angular frequency and the quality factor. The performance of the proposed circuit and its filter design application were examined by PSPICE simulations with TSMC 0.25-mm CMOS real process technology.

**Keywords:** Voltage Differencing Transconductance Amplifier (VDTA); Current Squarer; MOS analog circuits; Low-voltage circuits; Electronically tunable.

# Linearno nastavljiv CMOS napetostni transkonduktančni diferencialni ojačevalnik (VDTA)

Izvleček: Članek predlaga alternativno rešitev uporabe linearno nastavljivega CMOS napetostnega trnskonduktančnega diferencialnega ojačevalnika (VDTS). Načrtovan je z uporabo plavajočega tokovnega vira (FCS) in kvadriranjem toka. Vezje dosega linearno nastavljivost s kvadriranjem počasnega deleža toka FCS. Na ta način se lahko z nastavitvijo napajalnega toka linearno spreminja transkonduktančno ojačenje. Filter ima naslednje lastnosti: sočasna realizacija treh standardnih funkcij filtra, uporaba le dveh ozemljenih kondenzatorjev in elektronska nastaljivost wo in Q. Lastnosti so bile simuliranje v PSPICE okolju v TSMC 0.25-mm CMOS tehnologiji.

Ključne besede: napetostni transkonduktančni diferencialni ojačevalnik; (VDTA); tokovni kvadrirnik; analogna MOS vezja; nizkonapetostna vezja; elektronska nastavljivost

\* Corresponding Author's e-mail: drworapong@gmail.com

## 1 Introduction

A brief review of the recently reported active elements and an introduction to several new controllable elements are given in [1]. Among other things, the voltage differencing transconductance amplifier (VDTA) is one of attractive active devices with two-parameter control [2-6]. This device is a modified version of the previously introduced current differencing transconductance amplifier (CDTA) element, in which the current differencing unit at the input stage is replaced by the voltage differencing unit. Usually, the VDTA solution can be realized by composing two voltage-controlled current sources, which are interconnected internally. Each of them provides two independent transconductance gains ( $g_{mF}$  and  $g_{mS}$ ), which are electronically adjustable by external DC biasing currents [5]. Therefore, the VDTA element is very useful in active circuit synthesis and quite suitable for electronically controllable analog circuits. Another advantageous feature of this element is that it can easily be used for transconductance-mode solutions due to its input signals being voltages while the output signals are current [2]. Several CMOS reali-

zations of the VDTA circuit have been described in the literature [2-4]. Previously, the CMOS implementation of the VDTA employing basic floating current sources (FCSs) and supply voltages of ±0.9 V was introduced in [2]. The improved CMOS VDTA was suggested in [3], in which the ideal current sources are realized with swing cascade current mirrors. This kind of current mirrors is used because it has good accuracy and high-output impedance, and the minimum output voltage swing is approximated to 2V<sub>DS(sat)</sub> [7]. In [4], the design of the CMOS VDTA was also reported, where both transconductance sections were derived from the structure presented in [5]. In this structure, the well-known configuration of multiple-output second-generation current conveyor (MO-CCII) has been supplemented to obtain the required number of current outputs of the first transconductance section. However, their major disadvantage though is the well-known fact that their performance (namely the gain  $g_m$ ) is directly proportional to the square root function of the external DC biasing current. Due to this the tunability is non-linear, and their linear transconductance ranges are rather limited.

The motivation of this paper is to develop the CMOS VDTA with linearly tunable transconductance. To this aim, the proposed CMOS VDTA utilizes the floating current source (FCS) in its voltage-to-current conversion. In the presented work, the CMOS current squaring functional circuit with the output current proportional to the square of the input current is employed as a biasing circuit for the FCS. The main feature of the proposed VDTA is that it exhibits an ability to linearly tune its transconductane gains by electronic means through the external DC bias currents. To illustrate the application of the proposed VDTA, the design of active voltage-mode multifunction filter with single input and triple outputs is considered. It realizes simultaneously the three standard biquadratic filters namely lowpass (LP), bandpass (BP) and highpass (HP) from each output of the circuit. Orthogonal electronic programmability of  $\omega$  and Q is also discussed in detail. PSPICE simulations with TSMC 0.25- $\mu$ m CMOS process parameters are also reported, which demonstrate the linearity and effectiveness of the proposed VDTA and its application.

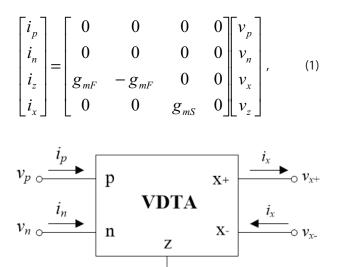

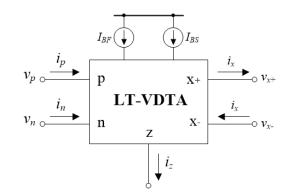

### 2 Basic concept of the VDTA

Basically, the VDTA is an alternative versatile active building block, having five high-impedance terminals, as symbolically shown in Fig.1. The characteristic between terminal voltages and currents can be described by the following matrix relation:

i.

Figure 1: Circuit symbol of the VDTA.

where  $g_{mF}$  and  $g_{mS}$  are the first and second transconductance gains of the VDTA, respectively. In (1), the differential input voltage applied across the p and n terminals ( $v_p - v_n$ ) is converted to a current flowing out of the z terminal ( $i_z$ ) by  $g_{mF}$ . Similarly, a voltage across the z terminal ( $v_z$ ) is transformed to the current outward from the x+ and x- terminals by  $g_{mS}$ .

### 3 Basic functional circuits

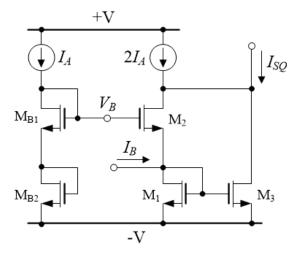

### 3.1 Current-squaring circuit

Fig.2 shows a current squaring circuit ( $M_1-M_3$ ) based on the square-law characteristic of MOS transistors biased in the strong inversion region [8-10]. The current-controlled biasing circuit ( $M_{B1}-M_{B2}$ ) is introduced in order to supply the bias voltage  $V_{B'}$  where  $I_A$  is the bias current. Assuming that all transistors are properly biased to operate in saturation mode and obey the ideal square-law function, the relation between the output current  $I_{SQ}$ and the input current  $I_B$  is given below.

$$I_{SQ} = \frac{I_B^2}{8I_A} \quad . \tag{2}$$

To guarantee a proper operation, the input current  $I_{_{B}}$  is restricted within the range:

$$-4I_A < I_B < 4I_A \quad . \tag{3}$$

Figure 2: Current squaring functional circuit.

We observe from eq. (2) that  $I_{sQ}$  is the squaring function of  $I_{B}$  with the gain equal to  $(1/8I_{A})$ . In addition to eq. (2), the current  $I_{sQ}$  is ideally temperature insensitive.

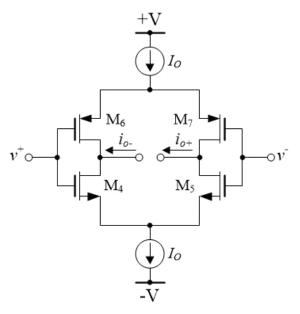

### 3.2 Floating Current Source

Fig.3 shows the circuit diagram of the floating current source (FCS) [11], which will be used as a fundamental circuit for exhibiting the transconductance gain of the proposed VDTA. The circuit can be viewed as two long-tailed differential pairs of PMOS and NMOS connected in parallel. It converts the differential input voltage ( $v_{id} = v^+ - v$ ) into two balanced output currents  $i_{o+}$  and  $i_o$ . The NMOS transistors  $M_4$  and  $M_5$  are identical and the PMOS transistors  $M_6$  and  $M_7$  are also identical. Assuming that all the transistors are working in saturation region, an effective small-signal transconductance of the FCS can be expressed as [11]:

$$g_{m} = \frac{i_{o+}}{v_{id}} = \frac{i_{o-}}{v_{id}} \cong \frac{g_{mn} + g_{mp}}{2} , \qquad (4)$$

where  $g_{mn}$  and  $g_{mp}$  are respectively the transconductance values of the NMOS and PMOS transistors, equal to :

$$g_{mn(p)} = \sqrt{K_{n(p)}I_O} \quad . \tag{5}$$

In above expression,  $K_{n(p)} = \frac{\mu_{n(p)}C_{ox}}{2} \frac{W}{L} \mu_{n(p)}$  is the average carrier mobility for NMOS and PMOS transistors,  $C_{ox}$  is the gate-oxide capacitance per unit area, W and L are the effective channel width and length, and  $I_o$  is the external DC bias current. Evidently from eqs.(4) and (5), the  $g_m$ -value of the FCS circuit in Fig.3 is proportional to a square-root of the control current  $I_o$ .

Figure 3: CMOS FCS circuit.

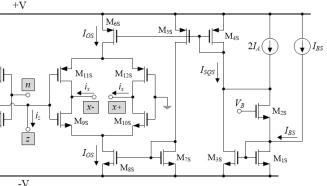

### 4 Proposed linearly tunable VDTA

A complete circuit diagram of the proposed linearly tunable VDTA (LT-VDTA) and its symbol are shown in Fig.4. Basically, it consists of two FCSs ( $M_{9F}-M_{11F}$  and  $M_{9S}-M_{11S}$ ) in Fig.3 and two current squaring circuits ( $M_{1F}-M_{3F}$  and  $M_{1S}-M_{3S}$ ) in Fig.2. The current-controlled DC level-shifting circuit  $M_{B1}-M_{B2}$  and  $I_A$  provide a bias voltage  $V_B$  for the circuit. As seen in Fig.4, the currents  $I_{OF}$  and  $I_{OS}$  of two FCSs by means of the current mirrors  $M_{4F}-M_{8F}$  and  $M_{4S}-M_{8S}$ , respectively. It can be arranged that if (W/L)<sub>6F</sub> = (W/L)<sub>5F</sub> = 8(W/L)<sub>4F</sub> and (W/L)<sub>6S</sub> = (W/L)<sub>5S</sub> = 8(W/L)<sub>4S</sub>, then, using eq.(2) and considering  $I_{OF} = 8I_{SOF}$  and  $I_{OS} = 8I_{SOS'}$  we have :

$$I_{OF} = \frac{I_{BF}^2}{I_A} \quad , \tag{6}$$

and

$$I_{OS} = \frac{I_{BS}^2}{I_A} \quad . \tag{7}$$

Substituting eqs.(6) and (7) into (5), and solving for the first and second transconductance gains of the proposed LT-VDTA in Fig.4, the results are :

$$g_{mF} = K_m I_{BF} \quad , \tag{8}$$

and

$$g_{mS} = K_m I_{BS} \quad , \tag{9}$$

where

(b)

$$K_m = \frac{\sqrt{K_n} + \sqrt{K_p}}{2\sqrt{I_A}} \quad . \tag{10}$$

(a) +VM<sub>6F</sub>  $I_{OF}$  $I_{BF}(\downarrow)$  $2I_A($ ISOF  $M_{12}$ p $M_{2F}$ M<sub>1</sub>  $I_{BF}$ IOF  $M_{1F}$ M<sub>3F</sub> M Me

**Figure 4:** Proposed CMOS VDTA with linearly transconductance tuning. (a) complete circuit diagram; (b) its circuit symbol

Since  $K_m$  is considered as a constant value, eqs.(8) and (9) imply that the transconductances  $g_{mF}$  and  $g_{mS}$  of the proposed LT-VDTA can be adjusted electronically and linearly by  $I_{BF}$  and  $I_{BS'}$  respectively. As was stated earlier, in order for the proposed circuit to operate correctly, the linear operating condition for the input controlling currents  $I_{BF}$  and  $I_{BS}$  is bounded according to eq.(3).

Owing to the performance of the traditional FCS stage used in the proposed LT-VDTA structure of Fig.4, the output resistances at terminals z, x+ and x- are not high enough for some applications. In order to increase the output resistance level, the improved FCS [12] can be employed for this structure. However, while the output resistance value is improved, the output voltage swing drops by up to  $V_{DSIGM}$ .

### 5 Simulations, results and discussions

For all the circuits examined in this work, the computer simulations with PSPICE are performed using model

parameters of TSMC 0.25- $\mu$ m CMOS technology. The transistor sizes used for simulation are listed in Table 1. Bias voltages were  $\pm$ V = 1.5 V and bias currents  $I_A$  were 50  $\mu$ A.

Table 1: Transistor sizes of the proposed LT-VDTA in Fig.4.

| Transistors                                                                                                                                                                                           | W (μm) | L (µm) |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|

| $\begin{array}{c} M_{B1} \text{ - } M_{B2} \text{,} \\ M_{1F} \text{ - } M_{2F} \text{, } M_{1S} \text{ - } M_{2S} \text{,} \\ M_{4F} \text{, } M_{4S} \text{, } M_{7F} \text{, } M_{7S} \end{array}$ | 7      | 0.25   |

| M <sub>3F</sub> , M <sub>3S</sub>                                                                                                                                                                     | 6      | 0.25   |

| M <sub>5F</sub> - M <sub>6F</sub> , M <sub>5S</sub> - M <sub>6S</sub>                                                                                                                                 | 49     | 0.25   |

| M <sub>8F</sub> , M <sub>8S</sub>                                                                                                                                                                     | 6.2    | 0.25   |

| M <sub>9F</sub> - M <sub>10F</sub> , M <sub>9S</sub> - M <sub>10S</sub>                                                                                                                               | 17     | 0.25   |

| M <sub>11F</sub> - M <sub>12F</sub> , M <sub>11S</sub> - M <sub>12S</sub>                                                                                                                             | 24     | 0.25   |

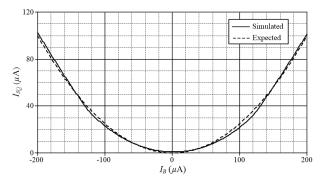

The CMOS current squaring circuit in Fig.2 is simulated. Fig.5 illustrates the DC current transfer curves of the current squaring circuit in Fig.2, obtained for the input controlling current  $I_{g}$  value ranging from -200  $\mu$ A to 200  $\mu$ A. It can be deduced from the simulation results that the circuit performs the current squaring operation as expected.

**Figure 5:** DC current transfer curves of the current squaring circuit in Fig.2.

In order to demonstrate the linear tuning performance of the proposed LT-VDTA in Fig.4, the simulation for the

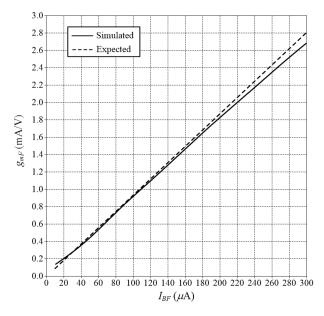

transconductance  $g_{mF}$  is carried out. Fig.6 shows the  $g_{mF}$  variations as a function of the input controlling current  $I_{BF}$ . In these plots, the simulated results and the expected values are compared, and in good agreement over a considerable input range from 20 µA to 180 µA. It is clear from the curves that the proposed circuit can be tuned linearly by means of the current  $I_{BF}$ .

**Figure 6**: Expected and simulated  $g_{mF}$  of the proposed LT-VDTA of Fig.4 as a function of  $I_{gF}$ .

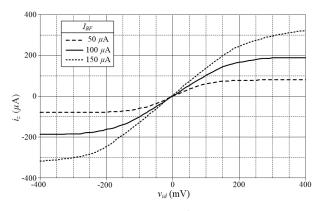

The DC transfer functions of the proposed LT-VDTA in Fig.4 are also simulated and shown in Fig.7, with  $v_{id}$  (=  $v_p - v_{n'}$ ) continuously changing from -400 mV to 400 mV, and  $I_{BF}$  being equal to 50  $\mu$ A, 100  $\mu$ A and 150  $\mu$ A, respectively. For  $I_{BF}$  = 150  $\mu$ A, the circuit has a linear region over ±180 mV and non-linearity error is less than 9.16%.

**Figure 7:** Simulated DC transfer characteristics between  $v_{id}$  and  $i_z$  with tuning  $l_{BF}$ .

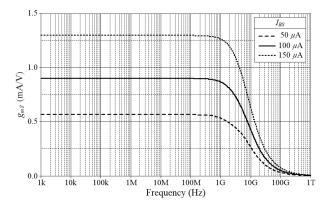

To study the AC transfer characteristic of the proposed LT-VDTA, the simulated frequency responses for  $g_{ms}$  when  $I_{BS}$  is swept from 50  $\mu$ A to 150  $\mu$ A with 50  $\mu$ A step

size are plotted in Fig.8. According to Fig.8, the useful bandwidth of about 400 MHz can be observed. In addition to the simulation results, the maximum power dissipation is 6.25 mW, when  $v_{id'} = 180$  mV, and  $I_{BF} = I_{BS}$  150  $\mu$ A. The quiescent power dissipation is 1.34 mW, when  $v_{id'}$   $I_{BF}$  and  $I_{BS}$  are zero.

**Figure 8:** Simulated frequency characteristics of  $g_{mS}$  with tuning  $I_{RS}$ .

# 6. Active voltage-mode multifunction filter realization

To demonstrate the effectiveness of the proposed LT-VDTA, an active voltage-mode multifunction filter of Fig.9 is realized as a design example [13]. The circuit consisting of two proposed LT-VDTAs in Fig.4 and two grounded capacitors realizes three standard biquadratic filtering functions, i.e. lowpass (LP), bandpass (BP) and highpass (HP), simultaneously without changing its configuration and without the need to impose component constraints. Straightforward analysis of Fig.9 using eq.(1) yields the following three voltage transfer functions.

$$H_{LP} = \frac{V_{LP}(s)}{V_{in}(s)} = H_0 \left(\frac{g_{mF2}g_{mS2}}{C_1 C_2}\right) \left[\frac{1}{D(s)}\right], \quad (11)$$

$$H_{BP} = \frac{V_{BP}(s)}{V_{in}(s)} = H_0 \left(\frac{g_{mF2}}{C_1}\right) \left[\frac{s}{D(s)}\right],\tag{12}$$

and

$$H_{HP} = \frac{V_{HP}(s)}{V_{in}(s)} = H_0 \left[\frac{s^2}{D(s)}\right],$$

(13)

where

$$H_{0} = \frac{g_{mF1}}{g_{mS1}},$$

(14)

$$D(s) = s^{2} + \left(\frac{g_{mF2}g_{mS2}}{g_{mS1}C_{1}}\right)s + \left(\frac{g_{mF1}g_{mF2}g_{mS2}}{g_{mS1}C_{1}C_{2}}\right), \quad (15)$$

and  $g_{mFi}$  and  $g_{mSi}$  (i = 1, 2) are respectively first and second transconductance gains of the *i*-th LT-VDTA. It follows from eqs.(11)-(15) that the natural angular frequency ( $\omega_o$ ) and the quality factor (Q) of the filter are

$$\omega_{o} = \sqrt{\frac{g_{mF1}g_{mF2}g_{mS2}}{g_{mS1}C_{1}C_{2}}} , \qquad (16)$$

and

**Figure 9:** Actively tunable voltage-mode multifunction filter realization using the proposed LT-VDTAs.

To achieve independent filter parameter control, a proper design can be developed by setting equal transconductances such that  $g_{m1} = g_{mF1} = g_{mS1}$  and  $g_{m2} = g_{mF2} = g_{mS2'}$  then  $\omega_o$  and Q from eqs.(16) and (17) turn to

$$\omega_o = \sqrt{\frac{g_{m2}}{C_1 C_2}} \quad , \tag{18}$$

and

$$Q = \frac{g_{m1}}{g_{m2}} \sqrt{\frac{C_1}{C_2}} \quad . \tag{19}$$

The parameter  $\omega_{o}$  can be tuned separately by changing  $g_{m2}$ . The transconductance ratio of  $g_{m1}$  and  $g_{m2}$  can be used for an adjustment of the parameter Q. However, if independent electronic control is needed, only  $g_{m1}$  could be used for Q control.

Furthermore, from eqs.(16) and (17), the active and passive sensitivities of  $\omega_{o}$  and Q can be expressed as:

$$S_{g_{mF1},g_{mF2},g_{mS2}}^{\omega_o} = -S_{g_{mS1}}^{\omega_o} = \frac{1}{2} , \quad S_{C_1,C_2}^{\omega_o} = -\frac{1}{2}$$

(20)

and

$$S^{\mathcal{Q}}_{g_{mF1},g_{mS1}} = -S^{\mathcal{Q}}_{g_{mF2},g_{mS2}} = \frac{1}{2} , \ S^{\mathcal{Q}}_{C_1} = -S^{\mathcal{Q}}_{C_2} = \frac{1}{2}$$

(21)

Both are low, and equal to 0.5 in magnitude.

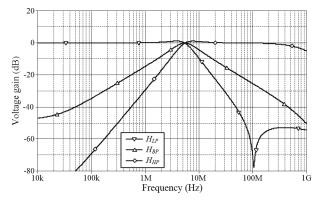

As a design example, the multifunction filter of Fig.9 has been realized to obtain the LP, BP and HP responses with the natural angular frequency  $f_o = \omega_o/2\pi \approx 5.50$  MHz and the quality factor Q = 1. For this purpose, the circuit components were set to:  $I_B = I_{BF1} = I_{BF1} = I_{BF2} = I_{BF2} = 70 \,\mu\text{A} (g_m = g_{mF1} = g_{mF1} = g_{mF2} = g_{mF2} \approx 0.66 \,\text{mA/V})$ , and  $C_1 = C_2 = 20 \,\text{pF}$ . The simulated LP, BP and HP amplitude responses of the circuit are shown in Fig.10, where the simulated values of  $f_o$  were found to have a maximum deviation of 2.83% from the expected values. In this simulation, the total power consumption of the designed filter is about 4.51 mW.

**Figure 10:** Simulated AC transfer responses for the actively voltage-mode multifunction filter in Fig.9.

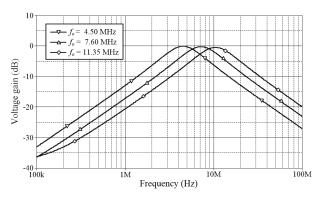

In Fig.11, the electronic adjustment of the BP characteristic is illustrated by simulating multiple values of  $f_o$  (i.e.  $f_o = 4.50$  MHz, 7.60 MHz, and 11.35 MHz), and keeping a constant Q = 1. Its responses for three values of  $f_o$  are obtained by tuning identical bias currents  $I_B = 50 \mu$ A, 100  $\mu$ A, and 150  $\mu$ A, respectively.

**Figure 11:** Simulated BP responses of Fig.9 with tuning f<sub>o</sub>.

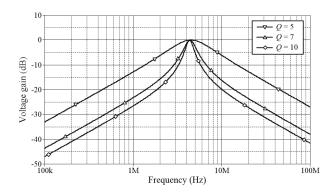

The simulation results of the BP response for variable Q and fixed  $f_o$  are given in Fig.12. In this way, the values of Q were tuned via LT-VDTA 1, for Q = 5, 7, 10, which correspond to  $I_{B1}$  (i.e.,  $I_{B1} = I_{BF1} = I_{BS1}$ ) = 250  $\mu$ A, 350  $\mu$ A, 500  $\mu$ A ( $g_{m1} \cong 2.40$  mA/V, 3.33 mA/V, 4.86 mA/V). A constant  $f_o = 4.50$  MHz was set with the bias currents of LT-VDTA 2, i.e.,  $I_{B2} = I_{BF2} = I_{BS2} = 50 \ \mu$ A ( $g_{m2} \cong 0.57$  mA/V).

Figure 12: Simulated BP responses of Fig.9 with tuning Q.

## 7 Conclusions

In this work, a linearly and electronically tunable CMOS VDTA circuit is realized. The circuit realization is based on floating current sources (FCSs) for implementing the transconductance stages. The CMOS current squaring circuit is used for supplying the long-tail bias current of the FCs stages. Its transconductance gains are linearly tuned and accurately determined by the external DC supplied currents. The use of the proposed VDTA is illustrated with a realization of an electronically tunable voltage-mode multifunction filter, which employs two VDTAs and two grounded capacitors. PSPICE simulations, performed using TSMC 0.35-µm CMOS technology and confirming the performance of the proposed circuit and its application, are also given.

### 8 Acknowledgements

This work was supported by King Mongkut's Institute of Technology Ladkrabang Research Fund [grant number KREF116001]. The author is grateful to Mr. Natchanai Roongmuanpha for his circuit simulation on an earlier version of the manuscript. Also, the author gratefully acknowledges the constructive comments and suggestions of all the anonymous reviewers, which have been very useful in the preparation of the revised version of the manuscript.

### 9 References

- D. Biolek, R. Senani, V. Biolkova, Z. Kolka, "Active elements for analog signal processing: classification, review, and new proposals", *Radioengineering*, vol.17, no.4, pp.15-32, 2008.

- 2. A. Yesil, F. Kacar, H. Kuntman, "New simple CMOS realization of voltage differencing transconductance amplifier and its RF filter application", *Radio-engineering*, vol.20, no.3, pp. 632-637, 2011.

- 3. A. Yesil, F. Kacar, "Electronically tunable resistorless mixed mode biquad filters", *Radioengineering*, vol.22, no.4, pp.1016-1024, 2013.

- J. Jerabek, R. Sotner, K. Vrba, "Electronically adjustable triple-input single-output filter with voltage differencing transconductance amplifier", *Rev. Roum. Sci. Techn.– Électrotechn. et Énerg.*, vol.59, no.2, pp.163-172, 2014.

- J. Satansup, W. Tangsrirat, "Compact VDTA-based current-mode electronically tunable universal filters using grounded capacitors, *Microelectron. J.*, vol.45, no.6, pp.613-618, 2014. https://doi.org/10.1016/j.mejo.2014.04.008

- 6. W. Tangsrirat, S. Unhavanich, "Voltage differencing transconductance amplifier-based floating simulators with a single grounded capacitor", *Indian J. Pure & Appl. Phys.*, vol.52, no.6, pp.423-428, 2014.

- 7. P. E. Allen, D. R. Holberg, *CMOS Analog Circuit Design*, New York : Oxford, 2002.

- K. Bult, H. Walliga, "A class of analog CMOS circuits based on the square-law characteristic of an MOS transistor in saturation", *IEEE J. Solid-State Circuits*, vol.SC-22, no.3, pp. 357-365, 1987. <u>https://doi.org/10.1109/jssc.1987.1052733</u>

- O. Landolt, E. Vittoz, P. Heim, "CMOS self-biased euclidean distance computing circuit with high dynamic range", *Electron. Lett.*, vol.28, no.4, pp.352-354, 1992. https://doi.org/10.1049/el:19920220

voltage reference by using a multiple differential

```

10. C. Popa, "CMOS logarithmic curvature-corrected

```

structure", Rev. Roum. Sci. Techn.– Électrotechn. et Énerg., vol.55, no.4, pp.436-444, 2010.

A. F. Arbel, L. Goladminz, "Output stage for current-mode feedback amplifiers, theory and applications", *Analog Integr. Circ. Signal Process.*, vol.2, no.3, pp. 243-255, 1992. <u>https://doi.org/10.1007/bf00276637</u>

M. Altun, H. Kuntman, "Design of a fully differential current-mode operational amplifier with improved input-output impedances and its applications", Int. J. Electron. Commun. (AEU), vol.62, no.3, pp. 239-244, 2008.

https://doi.org/10.1016/j.aeue.2007.03.020

J. Satansup, W. Tangsrirat, "Voltage-mode multifunction filter using VDTA and grounded capacitors", Proc. the 6th Conf. Electrical Eng. Network of Rajamangala University of Tech. 2014 (EENET 2014), pp.533-536, 2014.

Copyright © 2019 by the Authors. This is an open access article distributed under the Creative Com-

mons Attribution (CC BY) License (https://creativecommons.org/licenses/by/4.0/), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Arrived: 11. 04. 2019 Accepted: 21. 05. 2019 https://doi.org/10.33180/InfMIDEM2019.203

Journal of Microelectronics, Electronic Components and Materials Vol. 49, No. 2(2019), 69 – 77

# Simulation on the Interfacial Singular Stressstrain Induced Cracking of Microelectronic Chip Under Power On-off Cycles

Xiaoguang Huang

China University of Petroleum (East China), Department of Engineering Mechanics, Qingdao, China

**Abstract:** Thermal fatigue failure of a microelectronic chip usually initiates from the interface between the solder joint and substrate due to the mismatch in coefficients of thermal expansion (CTE). Because of the viscoelastic creep properties of the solders, the stress and strain at the solder/substrate interfaces are strongly dependent on temperature and time. Based on the established creep constitutive models of the solder materials, a three-dimensional thermomechanical analysis of the microelectronic chip undergoing power on-off cycles is conducted based on the finite element method (FEM). The singular interfacial stress-strain fields are obtained and the singular field parameters are quantitatively evaluated. Furthermore, the crack nucleation in power on-off fatigue test of the microelectronic chip is observed, to verify the conclusion that the singular stress-strain induces thermal fatigue failure from the solder/ substrate interface.

Keywords: Thermal fatigue; microelectronic chip; creep; singular field; crack nucleation

# Simulacija razpok mikroelektronskega čipa zaradi posameznih mejnih stresov pri ciklih vklapljanja napajanja

**Izvleček:** Različni termični koeficienti materialov so večinoma vzrok za odpvedi zaradi termične utrujenosti in pri čipu izhajano iz stične površine med lotom in substratom. Zaradi viskoelastičnosti lota je stress na mejni površini močno odvisen od časa in temperature. Uporabljena je tridimenzionalna termo-mehanična analiza vplivov ciklanja vklapljanja napajalne napetosti z uprabo metode končnih elementov. Kvantitativno so ocenjeni posamezni parametri in opažen je bil pojav nastajanja razpok zaradi stresa na stiku lot/substrat.

Ključne besede: termična utrujenost; mikoelektronski čip; polzenje; nastanek razpok

\* Corresponding Author's e-mail: huangupc@126.com

## 1 Introduction

The flip flat package technology is currently widely used in electronic engineering to meet the demands of high-speed functions and system miniaturization [1]. The high density and cost-effective requirements of the package structure have led to the emergence of small size and multiple input/output (IO) points in chip design. Solder joints, as the mechanical, electrical and heat-dissipating components, require excellent reliabilities during soldering and service [2-3]. In the soldering process, the formation of intermetallic compounds (IMCs) is a necessary condition for the formation of solder joints, and the reliability of solder joints is highly dependent on the formation and growth of IMC at the interface [4]. With the growth of intermetallic compounds, stress concentration easily appears at the interface of solder joint due to the mismatch of coefficients of thermal expansion of the materials, which causes the cracking and reduces the service life of solder joints [5-6]. Due to the increase of packaging density, both the size and shape of solder joints appear in various combinations, a quantitative evaluation method of the strength and life for solder joints is strongly expected.

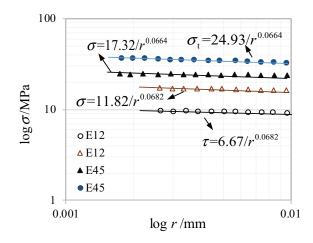

Under thermal cyclic loading, failure or fatigue crack generally initiates from the interface edge or near to the interface between the solder joint and substrate, and its mechanism is strongly affected by the stress singularity at the interface edge or stress concentration induced by the interface [7-9]. Therefore, it is of practical importance to determine the stress state at the interface, so that the susceptibility to thermomechanical failure can be predicted for new geometry-tomaterial combinations. The traditional strength-based methods are not suitable since the stresses are singular even at the idealized interface edges or corners [10-12]. To overcome this concern, Hattori et al. [13] have suggested a singularity parameter approach for the interface reliability of plastic IC packages using two stress intensity parameters that characterize the stress distribution near a bonded edge along with the interface. Other authors [14-16] argued that the two parameters: singular order  $\lambda$  and stress intensity factor K, can be used in a criterion for crack initiation or delamination for certain structure configurations. Generally, FEM is a valuable tool for determining the constants  $\lambda$  and K. At the same time, finite element modeling enables the design to be evaluated before it is physically produced thus minimizing time and cost. The results obtained from the FEM modeling will be useful in suggesting design changes in terms of package geometry and choice of packaging materials.

The purpose of this study is to develop an objective method to analyze the thermal cyclic behavior and to evaluate the failure of solder joints in a microelectronic chip. According to the creep results of solder materials, the nonlinear creep constitutive models are established. The three-dimensional thermomechanical analysis of the microelectronic chip under power on-off cycles is conducted, and the time-dependent stress and strain at the solder/substrate interfaces are obtained. Finally, the details that the singular stressstrain promotes the thermal fatigue failures from these interfaces are discussed when compared with the results from fatigue tests.

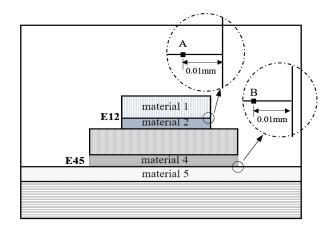

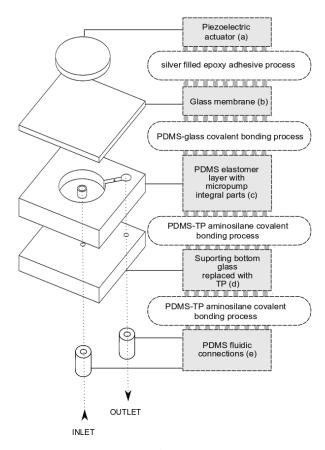

### 2 Package description

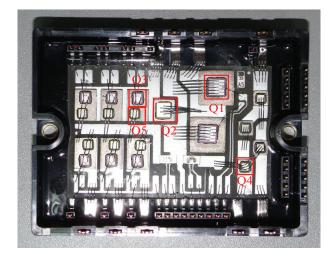

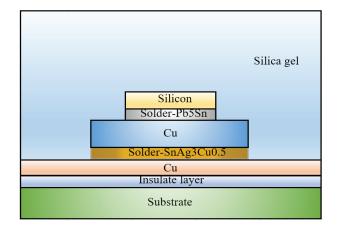

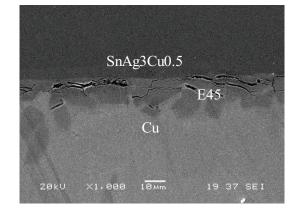

The structure of the microelectronic chipset is presented in Fig. 1. It has nineteen pieces of chips, including two pieces of chip Q1, one piece of chip Q2, six pieces of chip Q3, four pieces of chip Q4 and six pieces of chip Q5, respectively. Their working powers are 35.7, 33.3, 25.8, 20.0 and 14.5 w, respectively. The schematic crosssections of chip Q1-5 in layered structure are similar, i.e., substrate, insulate layer, Cu, SnAg3Cu0.5, Cu, Pb-5Sn, wafer and silica gel from bottom to top, as shown in Fig. 2. The main dimensions of chips Q1-5 are listed in Table1.

Figure 1: Structure of the microelectronic chipset

Figure 2: Schematic cross-section of the single chip

Table 1: Dimension of five different types of chips (unit: mm)

| Chip<br>type | Wafer<br>$A_0 \times B_0 \times C_0$ | Solder Pb-5Sn<br>A <sub>1</sub> ×B <sub>1</sub> ×C <sub>1</sub> | Solder<br>SnAg <sub>3</sub> Cu <sub>0.5</sub><br>A <sub>2</sub> ×B <sub>2</sub> ×C <sub>2</sub> |

|--------------|--------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Q1           | 6.6×6.6×0.38                         | 6.6×6.6×0.08                                                    | 13×13×0.12                                                                                      |

| Q2           | 5.4×5.4×0.46                         | 5.4×5.4×0.08                                                    | 8×8×0.12                                                                                        |

| Q3           | 3.6×4.2×0.38                         | 3.6×4.2×0.08                                                    | 8×11.5×0.12                                                                                     |

| Q4           | 3.3×3.3×0.25                         | 3.3×3.3×0.08                                                    | 5.5×5.5×0.12                                                                                    |

| Q5           | 3.2×3.2×0.46                         | 3.2×3.2×0.08                                                    | 8×11.5×0.15                                                                                     |

### 3 Numerical simulation process

### 3.1 Constitutive model of solder materials

According to the theory of viscoelasticity, the typical strain rate-stress relationship of the solder is linear at

low stress, and power law creep at middle and high stresses. On the basis of the previous literature [17-18], a hyperbolic sine power constitutive model is adopted, in which the relationship of strain rate with stress is linear at low stress and is hyperbolic sine power at middle and high stresses, as shown in Eq. (1). At each temperature *T*, there exists a critical stress  $\sigma_v$  (*T*), which is used to separate the linear and power law creep stages. According to the creep results of two solder materials Sn3Ag0.5Cu and Pb5Sn, the strain rates under various stress levels and temperature-dependent  $\sigma_v$  are determined, as shown in Table 2 [19].

Sn3Ag0.5Cu:

$$\dot{\varepsilon} = \begin{cases}

A(\sinh B\sigma)^n \exp(-H / RT) & \text{if } \sigma > \sigma_v \\

A_0 \exp(A_1 / T)\sigma \exp(-H / RT) & \text{if } \sigma \le \sigma_v \\

\end{cases}$$

(1)

Pb5Sn:

$$\dot{\varepsilon} = \begin{cases}

A(\sinh B\sigma)^n \exp(-H / RT) & \text{if } \sigma > \sigma_v \\

(A_0 - A_2(T - T_R))\sigma \exp(-H / RT) & \text{if } \sigma \le \sigma_v

\end{cases}$$

$$\sigma_{\rm V} = C_0 - C_1 (T - T_R) + C_2 (T - T_R)^2$$

<sup>(2)</sup>

where  $\sigma$  is the equivalent stress,  $\sigma_v$  is the linear viscous creep limit, *H* is the activation energy, *R* is the universal gas constant, *T* is the absolute temperature value, and  $T_e$  is 273 Kelvin (K).

#### 3.2 FEM analysis and results

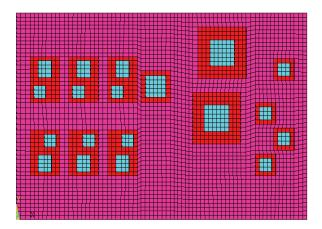

The FEM model of the whole chipset is shown in Fig. 3, and the related material constants are shown in Table 3.

Before the power-driven transient thermal analysis, the coefficients of heat transfer are determined by comparison of the temperatures obtained from numerical analysis and measured results in tests. The chipset maintains power on at the first 30 s, then power off. The measured temperature at the center of the bottom surface increases linearly from 21.2 °C to 70 °C within the first 19 s, keeps at 70 °C till 25 s, and decreases linearly from 70 °C to 35.2 °C within 25-44 s, finally maintains at 35.2 °C in the remained times. By adjusting the coefficients of heat transfer in the FEM model until the temperature at the center of the bottom and upper surfaces agree with the measured ones, the actual values of coefficients of heat transfer at the bottom and upper surfaces are finally determined.

Table 2: Material parameters and coefficients in Equations (1)-(2)

| Eq. (1)    | A (s <sup>-1</sup> ) | <i>B</i> (MPa⁻¹) | n    | <i>H/R</i> (K)                        | A₀ (MPa-1.s <sup>-1</sup> ) | <i>A</i> <sub>1</sub> (MPa) | A <sub>2</sub> (MPa) |

|------------|----------------------|------------------|------|---------------------------------------|-----------------------------|-----------------------------|----------------------|

| Sn3Ag0.5Cu | 2.08×106             | 0.145            | 5.85 | 12993                                 | 2.039×10-4                  | 8484                        |                      |

| Pb5Sn      | 3.16                 | 0.18             | 4.2  | 6535                                  | 8.168                       |                             | 0.0524               |

| Eq. (2)    | С <sub>0</sub> (МРа) |                  |      | C <sub>1</sub> (MPa.K <sup>-1</sup> ) |                             | C <sub>2</sub> (MP          | Pa.K⁻²)              |

| Sn3Ag0.5Cu | 17.357               |                  |      | 0.1219                                |                             | 2.457                       | ×10 <sup>-4</sup>    |

| Pb5Sn      | 8.0667               |                  |      | 0.00                                  | )17                         | 1.1364                      | ×10 <sup>-4</sup>    |

Table 3: Material constants in the analysis

| Material       | Elastic modu-<br>lus GPa | Poisson's<br>ratio | Coefficient of thermal<br>expansion<br>10 <sup>-6</sup> /K | Coefficient of heat<br>transfer<br>W/(m.K) | Density<br>kg/m³ | Specific Heat<br>J/( kg.m) |

|----------------|--------------------------|--------------------|------------------------------------------------------------|--------------------------------------------|------------------|----------------------------|

| Silicon        | 187.0                    | 0.25               | 5.05                                                       | 150.0                                      | 2330             | 678.262                    |

| Pb5Sn          | 16.1                     | 0.44               | 29.4                                                       | 35.2                                       | 11160            | 129.791                    |

| Cu             | 110.0                    | 0.35               | 16.5                                                       | 398.0                                      | 8960             | 385.186                    |

| SnAg3Cu0.5     | 41.6                     | 0.36               | 21.7                                                       | 64.2                                       | 7400             | 234.461                    |

| Cu             | 110.0                    | 0.35               | 16.5                                                       | 398.0                                      | 8960             | 385.186                    |

| Insulate layer | 5.4                      | 0.34               | 67.0                                                       | 4.0                                        | 3100             | 962.964                    |

| Al             | 73.0                     | 0.33               | 23.6                                                       | 237.0                                      | 2700             | 900.162                    |

| Substrate      | 0.1                      | 0.36               | 50.0                                                       | 0.17                                       | 980              | 1507.25                    |

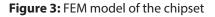

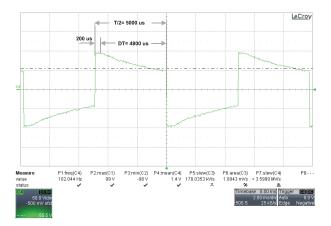

In the actual power-driven transient thermal analysis, the chipset is repeatedly powered on and off, and both the dwell times are 3 minutes. The transient thermal conduction analysis of the whole chipset is carried out at first, then followed by thermal stress submodel analysis of each chip according to the temperature fields obtained from the thermal conduction analysis of the whole chipset, to get the stress and strain distributions at the solder/substrate interfaces. The boundary conditions in the submodel of each chip are obtained by automatic interpolation of the ANSYS software, as shown in Fig. 4.

Figure 4: The detailed mesh and boundary conditions of chip Q1

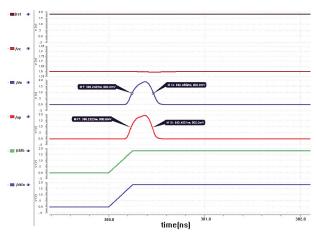

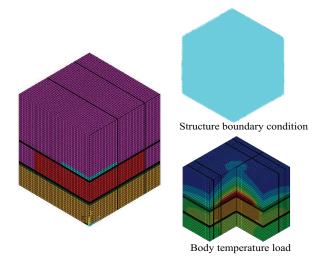

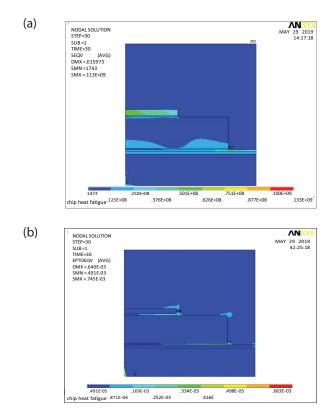

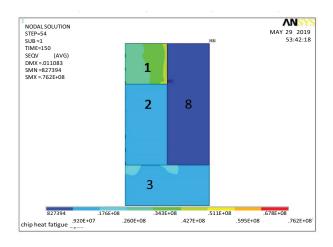

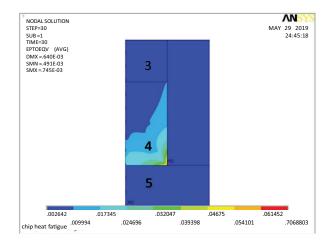

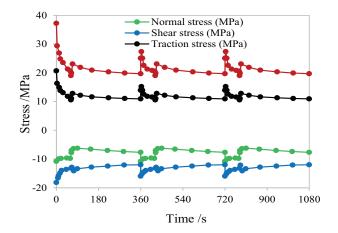

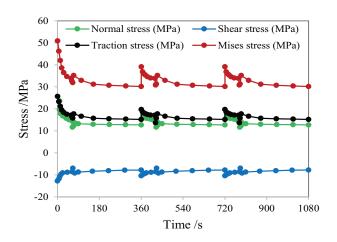

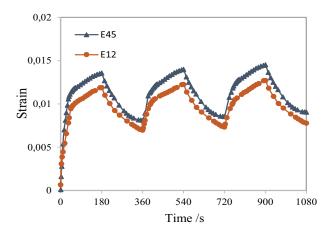

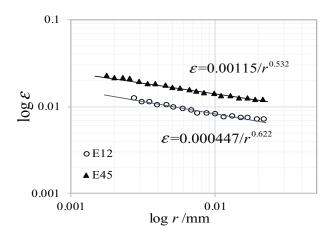

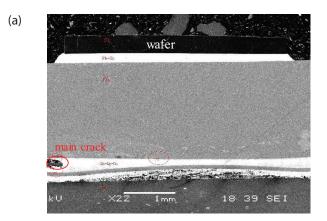

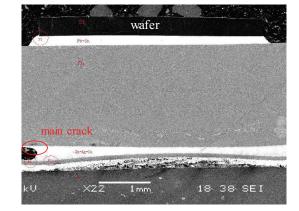

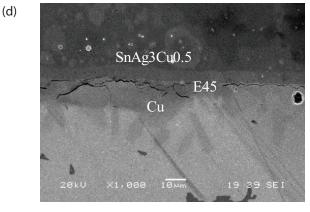

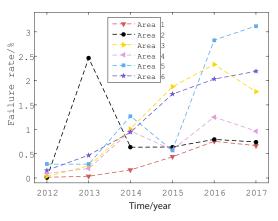

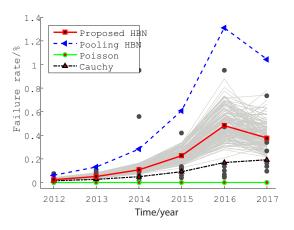

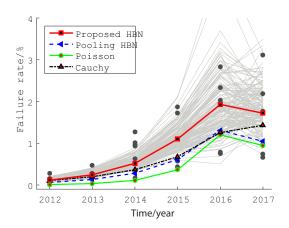

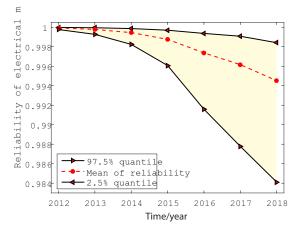

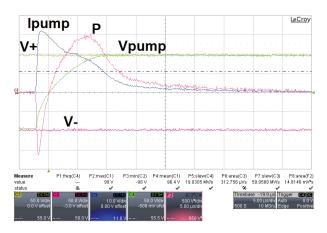

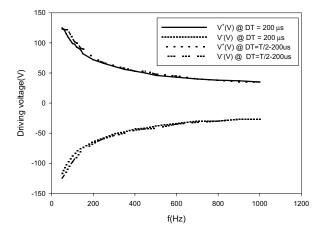

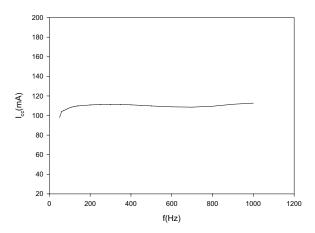

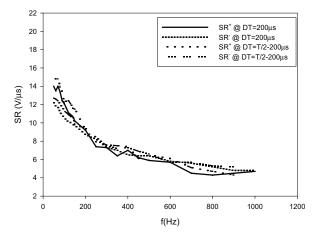

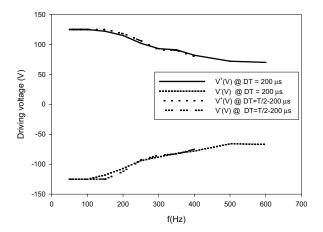

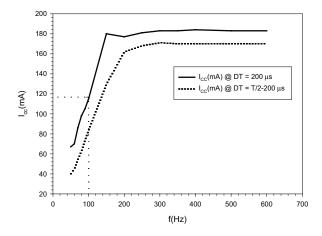

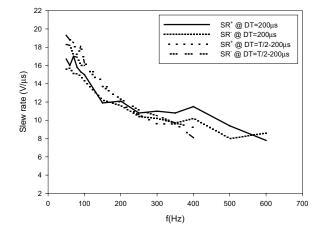

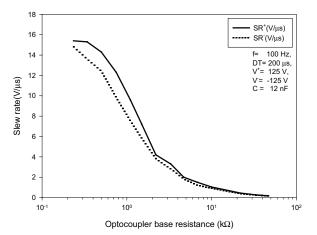

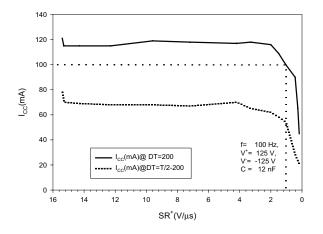

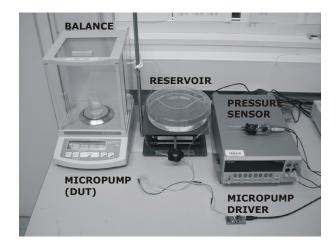

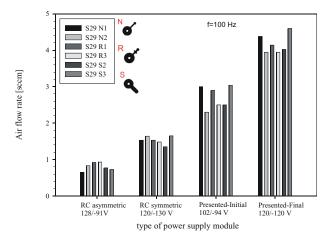

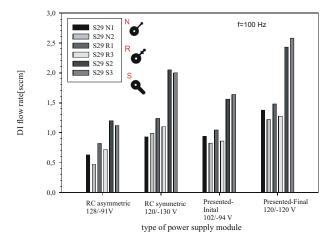

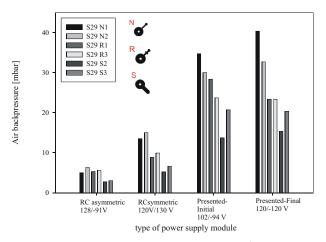

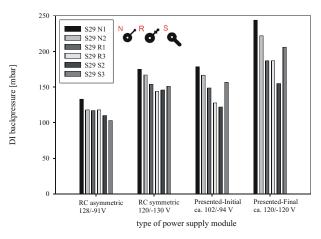

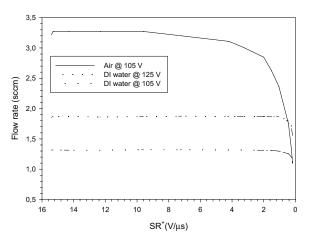

Fig. 5 shows the temperature and strain rate at the center of material 2 (solder Pb5Sn) and 4 (solder Sn3Ag0.5Cu). Due to the shock of power on, high temperature gradient and stress appear in solder Pb5Sn since it is just beneath the power layer. The high stress is presently relaxed because the strain rate reaches a balanced state. After the temperature gets to a saturated state, the strain rate decreases. Because the heat flux is difficult to pass through the thermal insulate layer (material 6) beneath it, the temperature gradient and stress in Sn3Ag0.5Cu solder are very small at the beginning of power on. Therefore, the strain rate at the initial state is very small and gradually increases with the rise of temperature. At the edges around the interface, the heat flux comes from the directions that are not blocked by the thermal insulate layer, as a result, the thermal shock appears. The instant thermal stress and strain distribution in the symmetry plane of chip Q1 at 30 s are shown in Fig. 6, it can be seen obvious stress and strain concentration at the interfacial edge between wafer and Pb5Sn (denoted by E12 in follows), and SnAg3Cu0.5 and Cu (denoted by E45 in follows).

**Figure 5:** Variations of temperatures and creep strain rates of the solders: (a) temperature, (b) creep strain rate (material 2: Pb5Sn, material 4: Sn3Ag0.5Cu)

**Figure 6:** Equivalent stress and strain distribution in the symmetry plane at 30 s: a) stress; b) strain