Informacije (MIDEM Journal of Microelec

Journal of Microelectronics, Electronic Components and Materials Vol. 47, No. 4(2017), 241 – 246

# A New Low-Power CMOS Sample-and-Hold Circuit Based on High-Speed Dynamic Body Biased Switches

Mohamad Hasan-Sagha and Mohsen Jalali

## Electrical Engineering Department, Shahed University, Tehran, Iran

**Abstract:** In this paper, a low-power open-loop CMOS sample-and-hold (S/H) circuit with improved linearity is presented. The incorporated switches utilize dynamic body connection technique to reduce distortions due to threshold voltage variations during track mode as well as signal feedthrough in the hold mode. To accomplish dual-edge sampling characteristic and differential operation, the proposed S/H circuit utilizes two pairs of the proposed switch and a 2:1 multiplexer. A current mode logic multiplexer without tail current is utilized to reduce power consumption while still fulfilling the speed and linearity requirements. The proposed S/H circuit is designed in a 90-nm CMOS process where it consumes approximately 610 µW from a 1.2 V supply voltage. Post-layout results show that a SFDR of about 73 dB is achieved when sampling a 1 GHz differential sinusoidal input at 2 GS/s rate using both edges of a 1 GHz clock signal.

Keywords: Sample and hold circuits; high-speed switches; body biasing; dual-edge sampling

# Novo vzorčevalno vezje nizke moči na osnovi hitrih dinamičnih stikal

**Izvleček:** Članek opisuje odprtozančno CMS vzorčevalno vezje nizke porabe z izboljšano linearnostjo. Vgrajena stikala vnašajo dinamično povezovalno tehniko za zmanjševanje distorcij pri nihanju pragovne napetosti v načinu sledenja, kakor tudi prenos signala v stanju zadržanja. Za zagotaljanje dvorobne vzorčevalne karakteristike in diferencialnega delovanja sta v predlaganem vzorčevalnem S/H vezju uporabljena dva para stikal in 2:1 multiplekser. V tokovnem načinu je uporabljen logični multiplekser za zniževanje porabe energije, pri čemer se hitrost in linearnost ohranjata. Predlagano S/H vezje je načrtano v 90 nm CMOS tehnologiji in pri napajalni napetosti 1.2 V porabi okoli 610 μW. Rezultati izkazujejo 73 dB SFDR pri vzorčenju z 2 GS/s in difenecialni sinusni vzorčevalni frekvenci 1 GHz.

Ključne besede: vzorčevalna vezja; stikala velikih hitrosti; dvorobno vzorčenje

\* Corresponding Author's e-mail: mjalali@shahed.ac.ir.

# 1 Introduction

High speed sample-and-hold (S/H) circuits have found many applications in emerging communication systems such as software defined radio, direct RF sampling receivers and sub-sampling RF architectures [1-3]. The S/H circuits are substantially classified into two main groups of closed-loop and open-loop configurations. There is a main trade-off between linearity and speed in both types. Closed-loop S/Hs [4], [5] are more linear than open-loop counterparts while open-loop S/Hs [6-8], on the other hand, have relatively higher speed, less power consumption and less circuit complexity [7]. However, in very high speed applications, distortions imposed by embedded switches seriously limit their application. Charge injection and signal feedthrough, in the hold mode, beside threshold voltage variation due to body effect along with amplitude and phase distortion due to finite channel resistance, in the track mode, are blamed as the main sources of distortions [9], [10].

Transmission gates implemented by parallel connection of PMOS and NMOS transistors are the simplest way to implement a CMOS switch. However, the unequal turn-on and turn-off delays of PMOS and NMOS transistors makes them suitable only for applications with moderate precisions especially when fast switching operation is required [11]. A vast varieties of bootstrap switches have been reported as linear and highprecision switches [12-14]. However, due to their circuit complexity and thus relatively lower speeds, they are not applicable in high speed applications. In this paper, a low-power high-speed sample-and-hold (S/H) circuit is proposed which takes the advantage of dynamic body connection technique to improve the linearity and speed of the incorporated switches. The paper is organized as follows; Section 2 illustrates the operation and analysis of the employed CMOS switches in details and then illustrates the implementation of the proposed S/H circuit. The results and discussion are provided in Section 3 followed by the conclusion in Section 4.

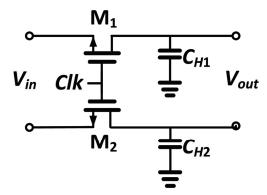

Figure 1: A simple differential CMOS switch

#### 2 Proposed S/H circuit

Shown in Fig. 1, a simple differential switch can be realized using a pair of nMOS (or pMOS) transistors  $M_{1'}$ ,  $M_2$  and holding capacitors  $C_{H1'}$ ,  $C_{H2'}$ . When the switch is conducting (Clk=1), the transistors are in deep triode region and exhibit a channel resistance of:

$$R_{ON} = \frac{1}{\mu_n C_{ox} S \left( V_{GS} - V_{ih} \right)}$$

(1)

where  $\mu_n$  is the electron mobility,  $C_{ox}$  is the gate-oxide capacitance, *S* denotes the transistor's aspect ratio and  $V_{GS}$  and  $V_{th}$  are gate-source voltage and threshold voltage, respectively. Reducing both  $R_{ON}$  and  $C_{H}$  results in better speed performance, however, a small  $C_{H}$  will significantly increases the impact of signal feedthrough on the sampled values leaving  $R_{ON}$  as the main means for alleviating the speed constraints. The simple switch shown in Fig. 1 also imposes phase and amplitude distortion during track mode mainly due to non-negligible switch resistance which can be evaluated as

$$\frac{V_{out}(j\omega)}{V_{in}(j\omega)} = \frac{1}{\sqrt{(\tau\omega)^2 + 1}} \exp\left(-j\tan^{-1}\tau\omega\right)$$

(2)

where  $\tau = R_{ON}C_{H}$  is the switch time constant.

Charge injection and clock feedthrough are other sources of distortion in CMOS switches. Methods such as differential design and using dummy transistor have been suggested [11] to mitigate these problems. However, in the case of differential design, each side of the differential switch receives different input voltage, which causes unequal impact of charge injection and clock feedthrough on each side that cannot be totally removed in a common mode scheme. Moreover, process-related variations also worsen the problem so that charge injection and clock feedthrough always partially impose inevitable residues at the output.

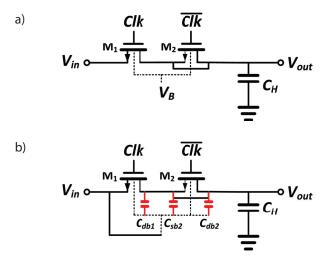

**Figure 2:** (a) MOS switch with constant body bias, (b) Signal feedthrough via parasitic capacitances when the body is connected to the source.

Shown in Fig. 2(a), to reduce the effects of non-idealities, there is benefits to using body-biasing technique. It is well-known that by applying a bias voltage to the bulk terminal of a MOS transistor, the threshold voltage decreases, which according to (1) and (2), lightens the amplitude and phase distortion. Obviously, the body bias voltage,  $V_{_{\rm B}}$ , should be applied to both switch transistor (M<sub>1</sub>) and the dummy transistor (M<sub>2</sub>) as it should be noted that an appropriate value for  $V_{B'}$  which allows for maximum input dynamic range with a symmetrical swing of at most 0.5 V, is the common-mode level of the input signal  $V_{in}$ . However, a problem which arises with applying a constant body bias to the bulk is that since the source-bulk voltage  $(V_{sh})$  of switch transistor varies with  $V_{in'}$  its threshold voltage depends on the input signal, acting as a main cause of distortion. This problem can be solved by connecting the bulk terminal to the source instead of connecting it to a constant voltage of V<sub>R</sub>. Nonetheless, an advantage of applying a positive voltage to the bulk, in comparison to tying the bulk to the source, is preventing the input signal to leak to the output through drain-bulk parasitic capacitance in the hold mode. To elaborate more on this issue, Fig. 2(b) schematically illustrates this problem indicating that the ratio of the leaked signal to the output is

$$\frac{V_{out}}{V_{in}} = \frac{C_1}{C_1 + C_H} \tag{3}$$

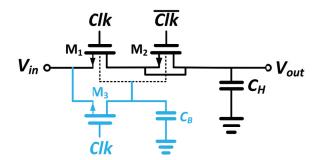

where  $C_1 = C_{BD1} + C_{BS2} + C_{BD2}$  in which  $C_{BD}$  and  $C_{BS}$  are drainbulk and source-bulk parasitic capacitances, respectively, so that subscripts 1 and 2 associate the parameters to  $M_1$  and  $M_{2'}$  respectively. The both mentioned problems of the threshold voltage variation of constant-body-biased switches and signal feedthrough of switches with their body connected to the source can be effectively solved using body-bias control circuit first introduced in [15], and modified and then called here as dynamic body bias (DBB) switch. Shown in Fig. 3, the  $M_3$  connects the body terminal of  $M_1$  to its source terminal during track mode thus preventing threshold voltage variation due to the body effect. During hold mode,  $M_3$  turns off disconnecting  $M_1$  body node from its source node avoiding signal feedthrough through drain-bulk parasitic capacitance.

**Figure 3:** MOS switch with dynamic body connection technique. M3 connects the body nodes to the input to prevent distortion due to threshold voltage variation.

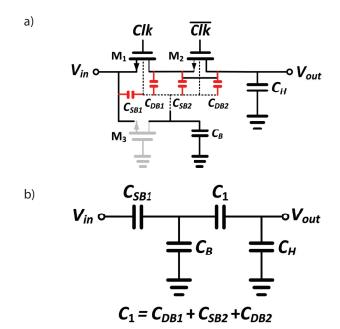

To analyze the feedthrough issue in the proposed DBB switch during hold mode (Clk=0), Fig. 4(a) shows how a capacitive coupling path between input and output is constructed by the parasitic capacitances of the  $M_1$  and  $M_2$ . The equivalent circuit of the parasitic path is shown in Fig. 4(b) where the amount of feedthrough can be expressed by

$$\frac{V_{out}}{V_{in}} = \frac{C_{BS1}.C_1}{C_B \left( C_1 + C_H \right) + C_H \left( C_{BS1} + C_1 \right) + C_{BS1}.C_1}$$

(4)

Since  $C_{_B}$  and  $C_{_H}$  are sufficiently larger than  $C_{_{BS1}}$  and  $C_{_{1'}}$  (4) simplifies to

$$\frac{V_{out}}{V_{in}} \approx \frac{C_{BS1}}{C_B} \frac{C_1}{\left(C_1 + C_H\right)}$$

(5)

**Figure 4:** (a) The signal feedthrough via parasitic capacitances of the proposed switch, (b) equivalent circuit of the parasitic path.

Comparing (5) with (3), the amount of feedthrough has been considerably reduced by a factor of  $C_{RC1}/C_{RC2}$ .

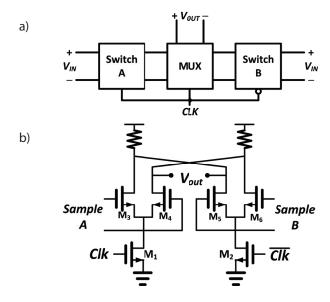

The dual edge triggered S/H circuit is realized using a pair of the proposed switch in differential configuration and a 2:1 multiplexer (MUX) circuit as conceptually illustrated in Fig. 5(a). The circuit is designed fully differential to improve its performance against common-mode distortions as well as supply and substrate noises [16]. Fig. 5(b) depicts the schematic circuit of

**Figure 5:** (a) The block diagram of the proposed dualedge triggered S/H, (b) schematic circuit of the 2:1 CML MUX.

the incorporated 2:1 MUX. A high-speed current mode logic (CML) MUX without any specific tail current is utilized. The reason is to reduce the number of stacked transistors allowing for higher output swing. The  $M_1$  and  $M_2$  operate as current switches working in deep triode region (when turned on) with a small drain-source voltage. In addition, since higher voltage headroom is now available for  $M_3$ - $M_{6'}$  their transconductances can be higher. In other words, we can reduce the sizes of these transistors while still having the same value of  $g_m$  comparing to the case with a specific tail current. Thus, the parasitic capacitances are reduced resulting in an improved speed.

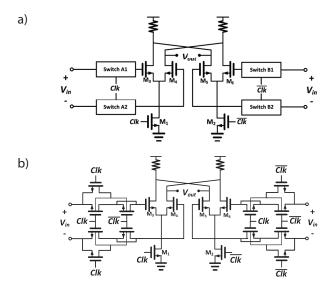

Fig. 6(a) shows the structure of the proposed S/H circuit. The operation of the circuit is as follows. On the rising edge of the Clk, the switches B1 and B2 turn off providing a sample of the input signal at their output. At the same time, the switches A1 and A2 are conducting and track the input signal. On the falling edge of the Clk, the input will be sampled by the switches A1 and A2. Thus, on each clock edges a sample of the input is provided and thus the 2:1 MUX can choose the samples on each proper switch output. The circuit implementation of the proposed S/H circuit is shown in Fig. 6(b). Each differential switch is implemented using a pair of DBB switch where no explicit holding capacitor (i.e.  $C_{\mu}$ and  $C_{\mu}$ ) is utilized. In fact, parasitic capacitances of the associated circuit nodes are sufficient for holding the samples over a short time.

**Figure 6:** (a) The structure of the proposed S/H circuit, (b) The schematic circuit of the proposed dual-edge triggered S/H circuit.

### 3 Simulation results

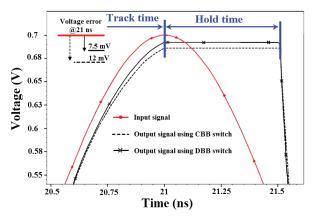

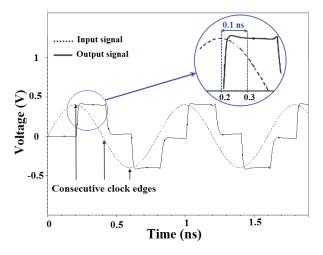

The proposed S/H circuit is implemented in a 90 nm CMOS process and post-layout simulations are carried out with a 1.2 V supply voltage while it consumes about 610  $\mu$ W. To evaluate the performance of the switches, Fig. 7 compares the outputs of the switch with constant body bias (CBB) (shown in Fig. 2(a)) and the switch with dynamic body bias (DBB) (depicted in Fig. 3) when taking samples from a 500 MHz sinusoidal input having 200 mV amplitude (over 0.5 V common mode level). Their sampled values include an error voltage of about 12 mV and 7.5 mV, respectively. The dynamic body bias switches offer higher speed and less distortion.

**Figure 7:** Comparison of samples taken by constant body bias (CBB) and dynamic body bias (DBB) switches.

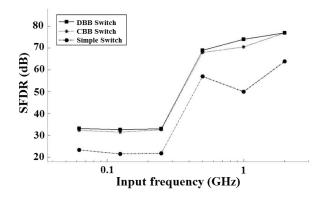

Fig. 8 indicates the SFDR of the proposed S/H circuit employing various switches, i.e. the simple switch (shown in Fig. 1) and the CBB and DBB switches, supposing a differential sinusoidal waveform with 0.2 V amplitude is applied to the inputs sampled at a rate of 2 GS/s. The SFDR at Nyquist rate when incorporating the proposed DBB switch is about 73 dB. If using CBB switch the SFDR drops to about 69 dB. For the sake of comparison, the SFDR if using simple nMOS switch is also shown that is about 48 dB. Obviously, the circuit that benefits from

**Figure 8:** SFDR of the proposed S/H circuit versus input frequency incorporating different switches.

proposed switch achieves better SFDR since threshold voltage variations are reduced.

**Table 1:** Performance summary of the proposed dual

edge triggered S/H circuit and its comparisons with

some prior work

sampling. The switches were optimized using dynamic body bias technique in order to reduce distortions. It utilizes a CML multiplexer at the output operating in a switching manner as a means for dual edge sampling. The proposed S/H has some advantages compared to other open-loop counterparts, such as low complexity,

| Design             | This work     | Ref. 3              | Ref. 6        | Ref. 8      | Ref. 5          | Ref. 7        |               |

|--------------------|---------------|---------------------|---------------|-------------|-----------------|---------------|---------------|

| Technology         | 90 nm         | 90 nm               | 0.35 μm       | 0.18 µm     | 0.35 µm         | 0.18 µm       | 0.35 μm       |

| Sampling rate      | 2 GS/s        | ~810 MS/s           | 250 MS/s      | 200 MS/s    | 400 MS/s        | 500 MS/s      | 250 MS/s      |

| Supply voltage     | 1.2 V         | 1.2 V               | _             | 1.8 V       | 2 V             | _             | _             |

| Power consumption  | 610 µW        | -                   | _             | 12.5 mW     | 6.7 mW          | _             | _             |

| SFDR               | 73dB@<br>1GHz | 27.3dB* @<br>~20GHz | _             | 76dB@200MHz | _               | _             | _             |

| Configuration type | Open-<br>loop | Open-loop           | Open-<br>loop | Open-loop   | Closed-<br>loop | Open-<br>loop | Open-<br>loop |

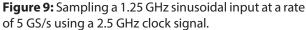

The output of the circuit in response to a 1.25 GHz sinusoidal input sampled at a rate of 5 GS/s is also shown in Fig.9. The delay from the clock edges to the time that the samples settle at the output implies that the whole circuit has less than 0.1 ns delay from input to the output. Table 1 shows the proposed S/H circuit performance summary and its comparison with other recently published CMOS realizations. The circuit do not have static power consumption and the input switches are fully passive without extra power consumption causing the overall circuit to operate with a lower power. The ability of the circuit to operate at a relatively high sampling rate mainly comes from appropriate MUX architecture and the optimized switches.

### 4 Conclusion

In this paper, a new architecture for open-loop S/H circuits was presented providing higher precision in

low-power operation and fully differential configuration.

## **5** References

- 1. R. Bagheri *et al.*, "An 800-MHz–6-GHz Software-Defined Wireless Receiver in 90-nm CMOS," in *IEEE Journal of Solid-State Circuits*, vol. 41, no. 12, pp. 2860-2876, Dec. 2006.

- M. Motoyosh, T. Koizum, T. Maehata, S. Kameda and N. Suematsu, "High SNR CMOS S/H IC for multi-carrier direct RF under sampling receiver," 2016 IEEE International Symposium on Radio-Frequency Integration Technology (RFIT), Taipei, 2016, pp. 1-3.

- J. Cheng, N. Qi, P. Y. Chiang and A. Natarajan, "A Low-Power, Low-Voltage WBAN-Compatible Sub-Sampling PSK Receiver in 65 nm CMOS," in *IEEE Journal of Solid-State Circuits*, vol. 49, no. 12, pp. 3018-3030, Dec. 2014.

- 4. T. Koizumi *et al.*, "A CMOS series/shunt switching type S/H IC for Ka-band direct RF under sampling receiver," *Asia-Pacific Microwave Conference* (*APMC*), Nanjing, 2015, pp. 1-3.

- 5. T. S. Lee, C. C. Lu, S. H. Yu, and J. T. Zha, A veryhigh-speed low-power low-voltage fully-differential CMOS sample-and-hold circuit with low hold pedestal, *Proc. IEEE Int. Symp. Circuits and Systems* (*ISCAS*) (2005), pp. 3111-3114.

- 6. M. Mousazadeh, K Hadidi, and A. Khoei, A novel open-loop high-speed CMOS sample-and-hold. *AEU-Int. Journal of Electronics and Communica-tions.* 62 (2008) 588-96.

- 7. K. D. Sadeghipour, A new passive sample and hold structure for high-speed, high-resolution ADCs. *AEU-Int. Journal of Electronics and Communications*. 65 (2011) 799-805.

- 8. A. Shirazi, S. Mirhaj, S. Ashtiani, and O. Shoaei, Linearity improvement of open-loop NMOS sourcefollower sample and hold circuits, *IET Circuits, Devices & Systems*. 5 (2011) 1-7.

- M. Hasan-Sagha, and M. Jalali, Very high speed and low voltage open-loop dual edge triggered sample and hold circuit in 0.18 µm CMOS technology, *Proc. IEEE Int. Conf. Semiconductor Electronics* (*ICSE*) (2012), pp. 645-648.

- 10. A. Boni, A. Pierazzi, and C. Morandi, A 10-b 185-MS/s track-and-hold in 0.35 μm CMOS, *IEEE J. Solid State Circuits.* 36 (2001) 195-203.

- 11. D. Jakonis, and C. Svensson, A 1GHz linearized CMOS track-and-hold circuit. *Proc. IEEE Int. Symp. Circuits and Systems (ISCAS)* (2002) pp. 1265-1277.

- 12. B. Razavi, Design of Analog CMOS Integrated Circuits (McGraw-Hill, New York, 2016).

- C. J. B. Fayomi, G. W. Roberts and M Sawan, Low voltage CMOS analog bootstrapped switch for sample-and-hold circuit: design and chip characterization, *Proc. IEEE Int. Symp. Circuits and Systems* (ISCAS) (2005) pp. 2200-2203.

- K. Ohhata, K. Yayama, Y. Shimizu and K. Yamashita, A 1-GHz, 56.3-dB SFDR CMOS track-and-hold circuit with body-bias control circuit, *Journal of IEICE Electronics Express*. 4 (2007) 701-706.

- G. Huang and P. lin, A fast bootstrapped switch for high-speed high-resolution A/D converter, *Proc. IEEE Asia Pacific Conf. Circuits and Systems* (2010) pp. 382-385.

- K. Ohhata, K. Yayam, Y. Shimizu and K. Yamashita, A 1-GHz, 56.3-dB SFDR CMOS track-and-hold circuit with body-bias control circuit, *Journal of IEICE Electronics Express* 4 (2007) 701-706.

- 17. H. Movahedian, B. Sedighi and M. S. Bakhtiar, Wide-range single-ended CMOS track-and-hold circuit, *Journal of IEICE Electronics Express* 4 (2007) 400-405.

Arrived: 18. 07. 2017 Accepted: 17. 10. 2017